## MCGRAW-HILL BEFERENCE

# PICNICROCONTROLLER Pocket Reference

- Key charts, protocols, and data tables

- Small trim, easy-to-scan layout

- Get all the facts and reference data

## MYKE PREDKO

PICmicro<sup>®</sup> Microcontroller Pocket Reference This page intentionally left blank.

## PICmicro<sup>®</sup> Microcontroller Pocket Reference

**Myke Predko**

**McGraw-Hill**

New York San Francisco Washington, D.C. Auckland Bogotá Caracas Lisbon London Madrid Mexico City Milan Montreal New Delhi San Juan Singapore Sydney Tokyo Toronto

## McGraw-Hill

#### A Division of The McGraw-Hill Companies

Copyright © 2001 by The McGraw-Hill Companies. All rights reserved. Manufactured in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the publisher.

#### 0-07-139563-6

The material in this eBook also appears in the print version of this title: 0-07-136175-8.

All trademarks are trademarks of their respective owners. Rather than put a trademark symbol after every occurrence of a trademarked name, we use names in an editorial fashion only, and to the benefit of the trademark owner, with no intention of infringement of the trademark. Where such designations appear in this book, they have been printed with initial caps.

McGraw-Hill eBooks are available at special quantity discounts to use as premiums and sales promotions, or for use in corporate training programs. For more information, please contact George Hoare, Special Sales, at george\_hoarc@mcgraw-hill.com or (212) 904-4069.

#### TERMS OF USE

This is a copyrighted work and The McGraw-Hill Companies, Inc. ("McGraw-Hill") and its licensors reserve all rights in and to the work. Use of this work is subject to these terms. Except as permitted under the Copyright Act of 1976 and the right to store and retrieve one copy of the work, you may not decompile, disassemble, reverse engineer, reproduce, modify, create derivative works based upon, transmit, distribute, disseminate, sell, publish or sublicense the work or any part of it without McGraw-Hill's prior consent. You may use the work for your own noncommercial and personal use; any other use of the work is strictly prohibited. Your right to use the work may be terminated if you fail to comply with these terms.

THE WORK IS PROVIDED "AS IS". McGRAW-HILL AND ITS LICENSORS MAKE NO GUARANTEES OR WARRANTIES AS TO THE ACCURACY, ADEQUACY OR COM-PLETENESS OF OR RESULTS TO BE OBTAINED FROM USING THE WORK. INCLUD-ING ANY INFORMATION THAT CAN BE ACCESSED THROUGH THE WORK VIA HYPERLINK OR OTHERWISE, AND EXPRESSLY DISCLAIM ANY WARRANTY, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. McGraw-Hill and its licensors do not warrant or guarantee that the functions contained in the work will meet your requirements or that its operation will be uninterrupted or error free. Neither McGraw-Hill nor its licensors shall be liable to you or anyone else for any inaccuracy, error or omission, regardless of cause, in the work or for any damages resulting therefrom. McGraw-Hill has no responsibility for the content of any information accessed through the work. Under no circumstances shall McGraw-Hill and/or its licensors be liable for any indirect, incidental, special, punitive, consequential or similar damages that result from the use of or inability to use the work, even if any of them has been advised of the possibility of such damages. This limitation of liability shall apply to any claim or cause whatsoever whether such claim or cause arises in contract, tort or otherwise.

DOI: 10.1036/0071395636

This page intentionally left blank.

## Contents

| Chapter 1. Conventions Used in This Book                               | 1   |

|------------------------------------------------------------------------|-----|

| Chapter 2. PICmicro <sup>®</sup> MCU Part Number<br>Feature Comparison | 3   |

| Feature to Part Number Table                                           | 3   |

| Chapter 3. Device Pinouts                                              | 7   |

| Low-End                                                                | 8   |

| Mid-Range                                                              | 10  |

| PIC17Cxx                                                               | 14  |

| PIC18Cxx                                                               | 17  |

| Chapter 4. PICmicro <sup>®</sup> MCU Instruction Sets                  | 21  |

| Parameters                                                             | 21  |

| Low-End Instruction Set                                                | 22  |

| Mid-Range Instruction Set                                              | 31  |

| PIC17Cxx Instruction Set                                               | 40  |

| PIC18Cxx Instruction Set                                               | 63  |

| Microchip Special Instruction Mnemonics                                | 104 |

| Parallax PICmicro <sup>®</sup> MCU Instruction Set                     | 111 |

## vi Contents

| Chapter 5. PICmicro <sup>®</sup> MCU Processor<br>Architectures | 123 |

|-----------------------------------------------------------------|-----|

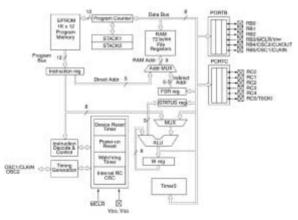

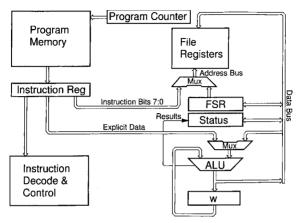

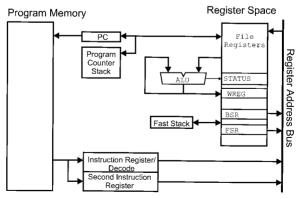

| Architectures                                                   | 123 |

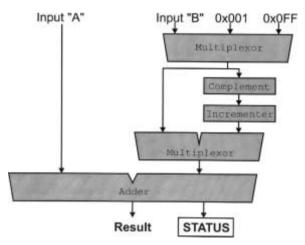

| The PICmicro <sup>®</sup> MCU's Arithmetic Logic Unit           | 123 |

| Low-End PICmicro <sup>®</sup> MCUs                              | 125 |

| Register access                                                 | 126 |

| STATUS register                                                 | 128 |

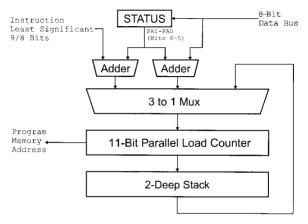

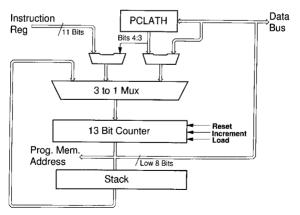

| Program counter                                                 | 128 |

| Mid-Range PICmicro <sup>®</sup> MCUs                            | 130 |

| Register access                                                 | 130 |

| STATUS register                                                 | 132 |

| Program counter                                                 | 133 |

| Interrupt operation                                             | 134 |

| Interrupt handler skeleton                                      | 135 |

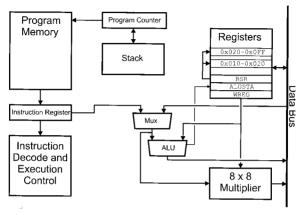

| PIC17Cxx                                                        | 136 |

| Register access                                                 | 137 |

| STATUS register                                                 | 138 |

| Program counter                                                 | 139 |

| Interrupt operation                                             | 140 |

| Interrupt handler skeleton                                      | 142 |

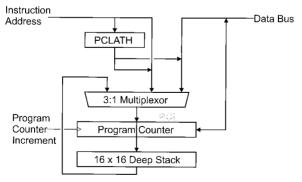

| PIC18Cxx                                                        | 142 |

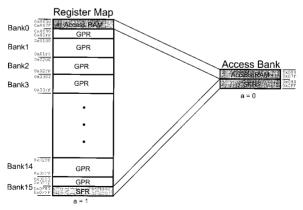

| Register access                                                 | 144 |

| STATUS register                                                 | 146 |

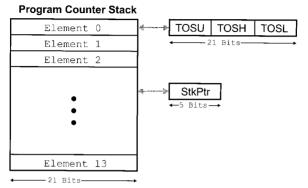

| Program counter                                                 | 147 |

| Interrupt operation                                             | 150 |

| Interrupt handler skeleton                                      | 150 |

| Chapter 6. PICmicro <sup>®</sup> MCU Register Mappings          | 151 |

| Low-End PICmicro <sup>®</sup> MCUs                              | 151 |

| Mid-Range PICmicro <sup>®</sup> MCUs                            | 154 |

| PIC17Cxx                                                        | 169 |

| PIC18Cxx                                                        | 186 |

| Contents                              | vii |

|---------------------------------------|-----|

| Chapter 7. Built-In Hardware Features | 207 |

| Configuration Registers               | 207 |

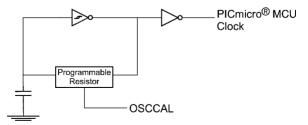

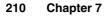

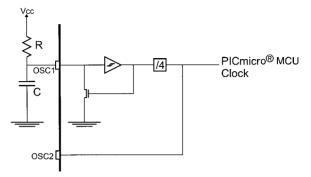

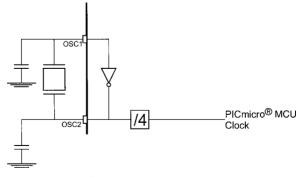

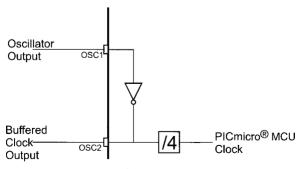

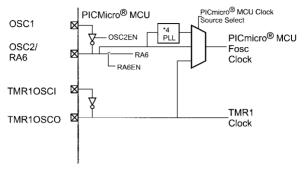

| Oscillators                           | 208 |

| Sleep                                 | 213 |

| Option Register                       | 216 |

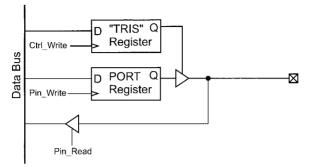

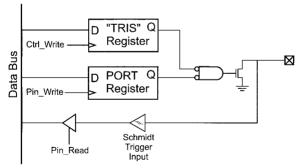

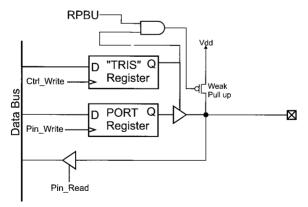

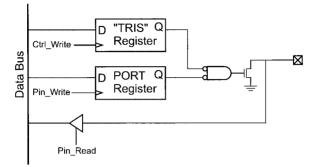

| Input/Output Ports and TRIS Registers | 217 |

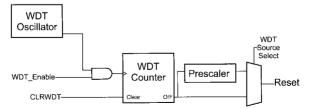

| Watchdog Timer                        | 221 |

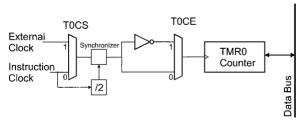

| TMR0                                  | 222 |

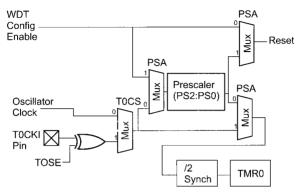

| Prescaler                             | 223 |

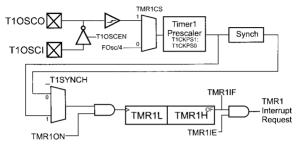

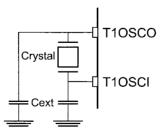

| TMR1                                  | 224 |

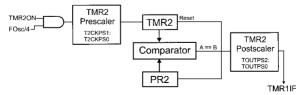

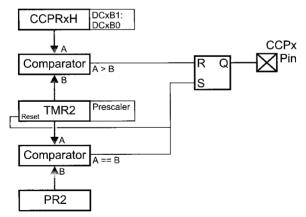

| TMR2                                  | 227 |

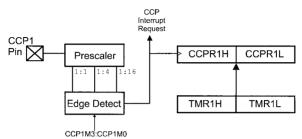

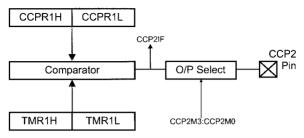

| Compare/Capture/PWM(CCP) Module       | 228 |

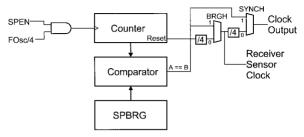

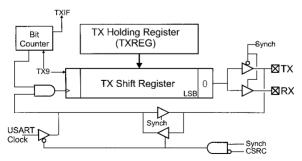

| USART Module                          | 232 |

| SSP Module                            | 239 |

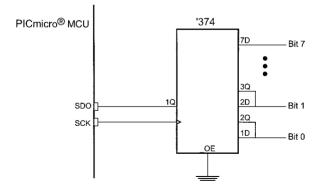

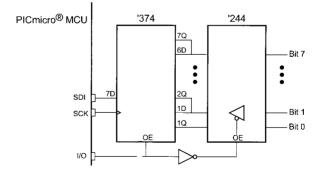

| SPI operation                         | 239 |

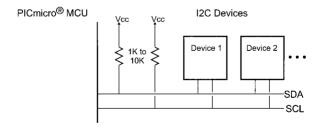

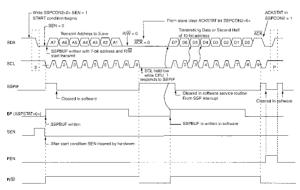

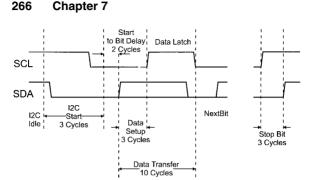

| I2C operation                         | 244 |

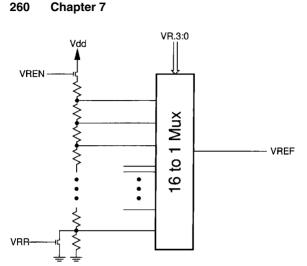

| Built-In ADC                          | 252 |

| Built-In Comparators                  | 257 |

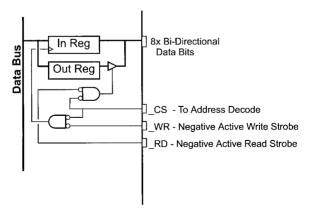

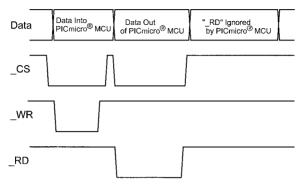

| Parallel Slave Port                   | 261 |

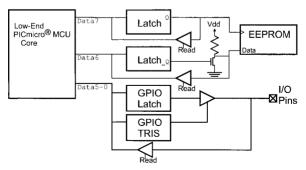

| Built-In EEPROM Data Memory Access    | 263 |

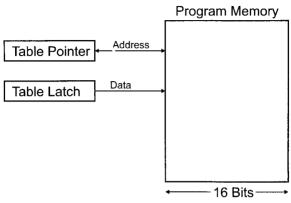

| EPROM Program Memory Access           | 269 |

| Flash Program Memory Access           | 271 |

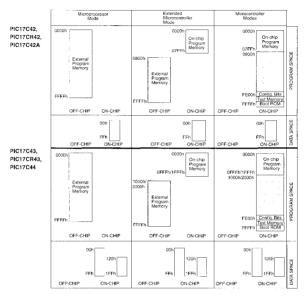

| External Parallel Memory              | 273 |

| Chapter 8. PICmicro <sup>®</sup> MCU  |     |

| Hardware Interfacing                  | 277 |

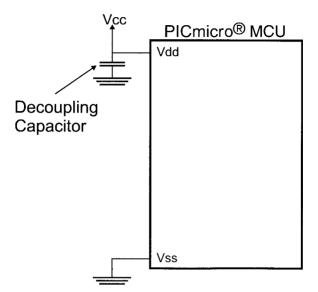

| Power                                 | 277 |

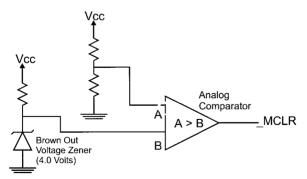

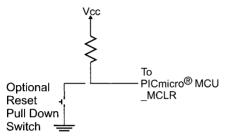

| Reset                                 | 281 |

| Digital Logic Interfacing             | 282 |

## viii Contents

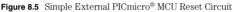

| Parallel Bus Device Interfacing                  | 282 |

|--------------------------------------------------|-----|

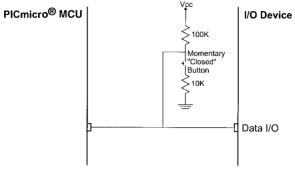

| Button Interfacing                               | 284 |

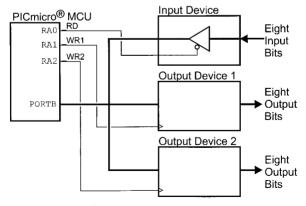

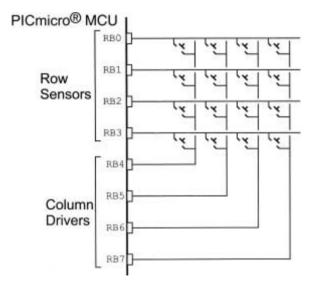

| Switch Matrix Keypad/Keyboard Interfacing        | 287 |

| Combining Input and Output                       | 291 |

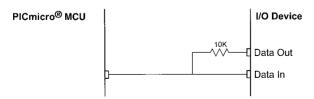

| Simulated "Open Collector"/"Open Drain" I/O      | 292 |

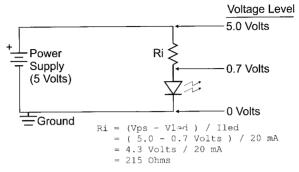

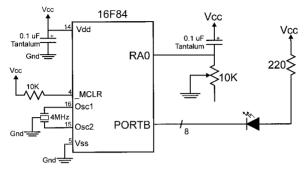

| LEDs                                             | 293 |

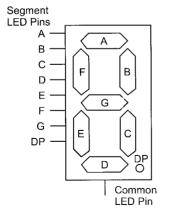

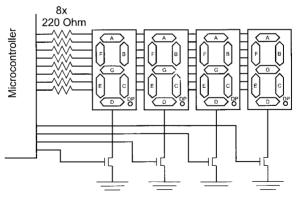

| Multisegment LED displays                        | 293 |

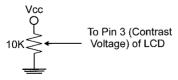

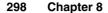

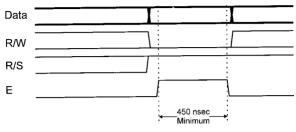

| LCD Interfaces                                   | 296 |

| I2C Bit Banging "Master" Interface               | 334 |

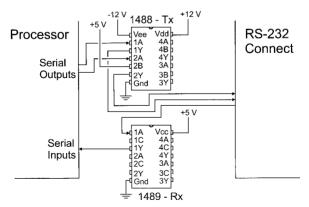

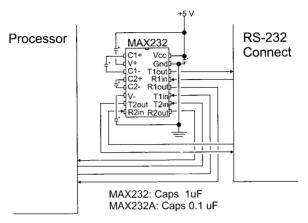

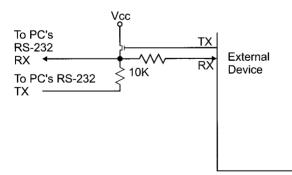

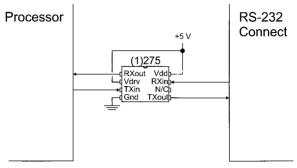

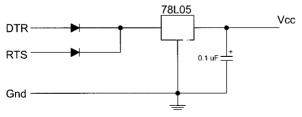

| RS-232 Interfaces                                | 338 |

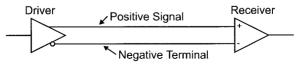

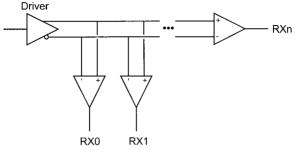

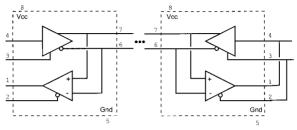

| RS-485/RS-422                                    | 345 |

| Asynchronous Serial I/O Software Routines        | 347 |

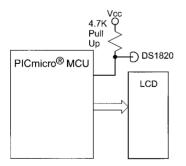

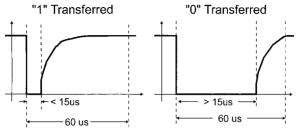

| Dallas Semiconductor One-Wire Interface          | 357 |

| Reading Potentiometer Using Parallel I/O Pins    | 363 |

| Motor Drivers                                    | 365 |

| R/C Servo Control                                | 370 |

| Audio Output                                     | 371 |

| AC Power Control                                 | 373 |

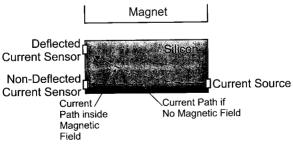

| Hall-Effect Sensors                              | 374 |

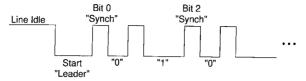

| Sony Infrared TV Remote Control                  | 374 |

| Chapter 9. PICmicro <sup>®</sup> MCU Programming | 379 |

| "Hex" File Format                                | 379 |

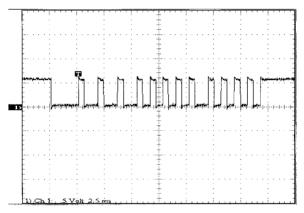

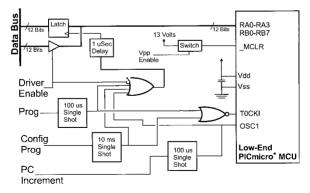

| Low-End PICmicro <sup>®</sup> MCU Programming    | 381 |

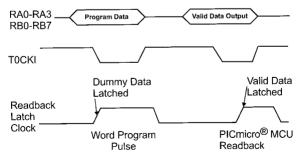

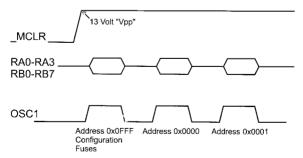

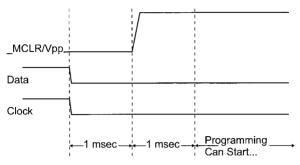

| Mid-Range Serial Programming                     | 385 |

| PIC17Cxx Programming                             | 394 |

| PIC17Cxx ICSP Programming                        | 398 |

| PIC18Cxx Programming                             | 402 |

| Microchip ICSP Programming Connector             | 405 |

| Third Party/Downloadable Programmers             | 406 |

|                                                  |     |

| Chapter 10. PC Interfaces                    | 407        |

|----------------------------------------------|------------|

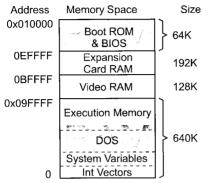

| Memory Map                                   | 407        |

| I/O Space Map                                | 407        |

| Interrupt Function by Number                 | 422        |

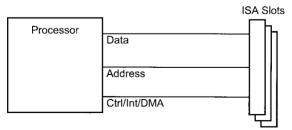

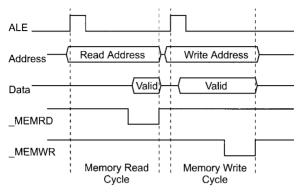

| ISA Bus                                      | 425        |

| ISA pinouts                                  | 425        |

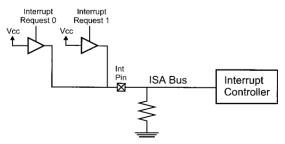

| Interrupts                                   | 429        |

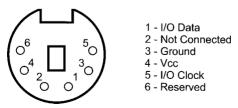

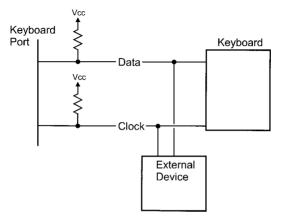

| Keyboard and Mouse Ports                     | 430        |

| Connector specification                      | 430        |

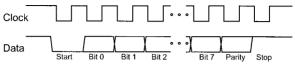

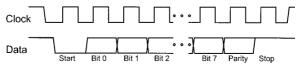

| Keyboard operation with timing diagrams      | 431        |

| Keyboard scan codes                          | 432        |

| Keyboard controller commands                 | 436        |

| BIOS interfaces                              | 436        |

| Keyboard commands                            | 441        |

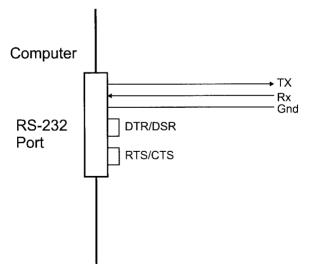

| Serial Port                                  | 441        |

| Connector pinouts                            | 442        |

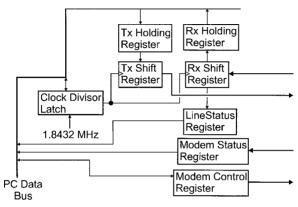

| 8250 block diagram                           | 443<br>443 |

| Serial port base addresses<br>8250 registers | 443        |

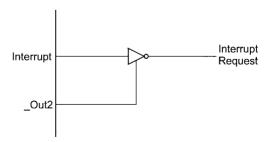

| Interrupts                                   | 444        |

| Interrupt 14h–RS-232 communications APIs     | 451        |

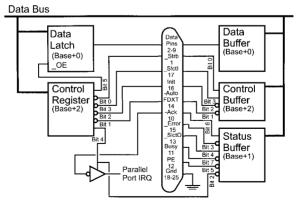

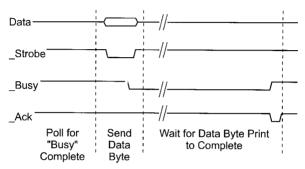

| Parallel Port                                | 455        |

| Block diagram/connector                      | 455        |

| Base registers                               | 457        |

| Registers                                    | 457        |

| Data output waveform                         | 458        |

| BIOS interfaces                              | 459        |

| Chapter 11. Useful Code "Snippets"           | 461        |

| Jumping Outside the Current Page             | 461        |

| Tables                                       | 462        |

| Conditional Branching | 465 |

|-----------------------|-----|

| j                     |     |

## x Contents

| Time Delays                              | 466 |

|------------------------------------------|-----|

| Negating the Contents of a Register      | 467 |

| Incrementing/Decrementing "w"            | 468 |

| Rotating a Byte in Place                 | 469 |

| Copy Bits from One Register to Another   | 470 |

| Converting a Nybble to ASCII             | 470 |

| Converting an ASCII Byte to a Hex Nybble | 471 |

| Using T0CKI as an Interrupt Source Pin   | 471 |

| Dividing by Three                        | 472 |

| Sixteen-Bit Pulse Measurement with       |     |

| 5-Cycle Delay                            | 473 |

| Detect a Change in a Register            | 474 |

| Test a Byte within a Range               | 474 |

| Convert ASCII to Upper Case              | 475 |

| Swap the Contents of "w" with a Register | 475 |

| Swap the Contents of Two Registers       | 475 |

| Compare and Swap if $Y < X$              | 476 |

| Counting the Number of "1"s in a Byte    | 476 |

| Generating Parity for a Byte             | 477 |

| Keeping a Variable within a Range        | 477 |

| Swapping Bit Pairs                       | 478 |

| Bitwise Operations                       | 478 |

| Constant Multiplication                  | 479 |

| Constant Division                        | 480 |

|                                          |     |

|                                          |     |

## Chapter 12. 16-Bit Numbers 483

| Defining 16 Bit Numbers                       | 483 |

|-----------------------------------------------|-----|

| Increments and Decrements                     | 484 |

| Addition/Subtraction                          | 485 |

| Bitwise Operations on Constants and Variables | 488 |

|                                                                            | Contents    | xi  |

|----------------------------------------------------------------------------|-------------|-----|

| Comparisons with 16-Bit Variables                                          |             | 489 |

| Multiplication                                                             |             | 492 |

| Division                                                                   |             | 495 |

| Chapter 13. PICmicro <sup>®</sup> MCU                                      |             |     |

| Operations Tables                                                          |             | 499 |

| I/O Pin Current Capabilities                                               |             | 500 |

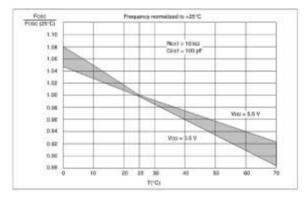

| RC Oscillator Component Values                                             |             | 500 |

| LP Oscillator Operating Characterist                                       | ics         | 501 |

| XT Oscillator Operating Characterist                                       | ics         | 502 |

| HS Oscillator Operating Characterist                                       | ics         | 504 |

| Chapter 14. PICmicro <sup>®</sup> MCU Applica<br>Debugging Checklist       | ation       | 507 |

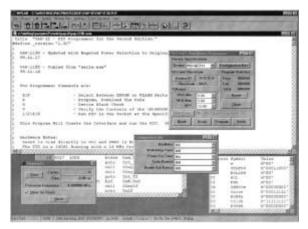

| Chapter 15. PICmicro <sup>®</sup> MCU Applic<br>Software Development Tools | ation       | 517 |

| Microsoft Compatible Editor "Ctrl" K                                       | ev          |     |

| Combinations                                                               | -,          | 517 |

| MPSIM.INI                                                                  |             | 518 |

| MPLAB                                                                      |             | 519 |

| Stimulus (.STI) files                                                      |             | 525 |

| MPLAB assembler directives                                                 |             | 526 |

| Standard Declaration and Include (".                                       | inc") Files | 536 |

| Linking–Linked Applications                                                |             | 536 |

| Application Code Template                                                  |             | 539 |

| The BASIC Language                                                         |             | 540 |

| Microsoft BASIC Enhancements                                               |             | 542 |

| PicBasic                                                                   |             | 549 |

## xii Contents

| Visual Basic                                    | 578 |

|-------------------------------------------------|-----|

| MSComm control                                  | 581 |

| The "C" Language                                | 588 |

| Declarations                                    | 588 |

| Statements                                      | 590 |

| Operators                                       | 593 |

| Directives                                      | 595 |

| "Backslash" characters                          | 598 |

| Common C functions                              | 598 |

| PICmicro <sup>®</sup> MCU enhancement functions | 603 |

| Chapter 16. Constants and Data Tables           | 605 |

| Mathematical and Physical Constants             | 605 |

| ASCII                                           | 606 |

| ASCII control characters                        | 607 |

| ANSI display control sequences                  | 609 |

| IBM PC extended ASCII characters                | 612 |

| Windows ASCII characters                        | 612 |

| EBCDIC                                          | 612 |

| Audio Notes                                     | 615 |

| "Touch-Tone" Telephone Frequencies              | 616 |

| Modem "AT" Commands                             | 616 |

| Modem registers                                 | 622 |

| Morse Code                                      | 625 |

| Phonetic Alphabets                              | 626 |

| "Ten" Radio Codes                               | 626 |

| Chapter 17. Miscellaneous Electronics           | 629 |

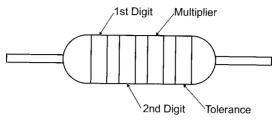

| Resistor Color Coding                           | 629 |

| Electromagnetic Spectrum                        | 630 |

| Radar bands                                     | 632 |

| Cont                                            | tents xiii |

|-------------------------------------------------|------------|

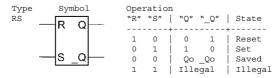

| Digital Logic                                   | 632        |

| Gates                                           | 632        |

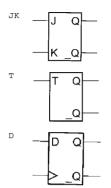

| Flip flops                                      | 633        |

| Chapter 18. Formulas                            | 635        |

| DC Electronics Formulas                         | 635        |

| AC Electronics Formulas                         | 636        |

| Mathematical Formulas                           | 638        |

| Boolean Arithmetic                              | 638        |

| Conversions                                     | 640        |

| Chapter 19. Resources                           | 641        |

| Microchip                                       | 641        |

| PICmicro <sup>®</sup> MCU Books                 | 642        |

| Useful Books                                    | 643        |

| PICList Internet List Server                    | 648        |

| Recommended PICmicro <sup>®</sup> MCU Web Sites | s 656      |

| Periodicals                                     | 658        |

| Useful Web Sites                                | 659        |

| Hardware FAQs                                   | 660        |

| Part Suppliers                                  | 661        |

| Digi-Key                                        | 661        |

| AP Circuits                                     | 661        |

| Wirz Electronics<br>Tower Hobbies               | 662        |

| Jameco                                          | 663<br>663 |

| JDR                                             | 663        |

| Newark                                          | 664        |

| Marshall Industries                             | 664        |

| Mouser Electronics                              | 665        |

| Mondo-tronics Robotics Store                    | 665        |

This page intentionally left blank.

## Conventions Used in This Book

| Hz     | Hertz (Cycles per Second)                  |

|--------|--------------------------------------------|

| kHz    | Kilohertz (Thousands of Cycles per Second) |

| MHz    | Megahertz (Millions of Cycles per Second)  |

| GHz    | Gigahertz (Billions of Cycles per Second)  |

| bps    | Bits per Second                            |

| kbps   | Thousands of Bits per Second               |

| mbps   | Millions of Bits per Second                |

| KBytes | 1,024 Bytes                                |

| MBytes | 1,048,576 Bytes                            |

| GBytes | 1,073,741,824 Bytes                        |

| К                                        | 1,000 ohms                                                                                                                                    |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| uF<br>ms/msecs<br>us/usecs               | microfarads<br>milliseconds<br>microseconds                                                                                                   |

| 0x0nn, \$nn,<br>0nnh, and<br>H'nn'       | Hex Numbers                                                                                                                                   |

| 0b0nnn,<br>%nnn,<br>0nnnb, and<br>B'nnn' | Binary Number                                                                                                                                 |

| nnn, 0nnnd,<br>and .nnn                  | Decimal Number                                                                                                                                |

| AND and &<br>OR and  <br>XOR and ^       | Bitwise "AND"<br>Bitwise "OR"<br>Bitwise "XOR"                                                                                                |

| _Label                                   | Negative Active Pin. In some manufacturer's data sheets this is represented with a leading "!" character or with a bar over the entire label. |

| [parameter]                              | The parameter is optional.                                                                                                                    |

| parameter  <br>parameter                 | One or another parameter can be used.                                                                                                         |

## PICmicro<sup>®</sup> MCU Part Number Feature Comparison

## Feature to Part Number Table

The following table lists the different PICmicro<sup>®</sup> MCU families with the features that are specific to them.

Copyright 2001 The McGraw-Hill Companies. Click Here for Terms of Use.

| Part Number | Features                                                                                                                                                        |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIC12C5xx   | 8-Pin PICmicro <sup>®</sup> MCU. 12-Bit (Low-End) Processor. Internal Reset & Oscillator.                                                                       |

| PIC12C6xx   | 8-Pin PICmicro <sup>®</sup> MCU. 14-Bit (Mid-Range) Processor. 8-Bit ADC/Internal<br>Reset & Oscillator/Optional EEPROM Data Memory.                            |

| PIC14C000   | 28-Pin PICmicro® MCU. 14-Bit (Mid-Range) Processor. Advanced<br>ADC/Internal Voltage Reference/On Chip Temperature Sensor.                                      |

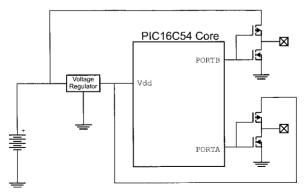

| PIC16C5x    | 18- to 28-Pin PICmicro <sup>®</sup> MCU. 12-Bit (Low-End) Processor.                                                                                            |

| PIC16C505   | 14-Pin PICmicro <sup>®</sup> MCU. 12-Bit (Low-End) Processor. Internal Reset & Oscillator.                                                                      |

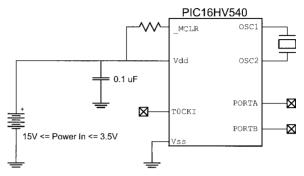

| PIC16HV540  | 18-Pin PICmicro <sup>®</sup> MCU. 12-Bit (Low-End) Processor. Extended Vdd<br>Capabilities with Built-In Regulator.                                             |

| PIC16C55x   | 18-Pin PICmicro <sup>®</sup> MCU. 14-Bit (Mid-Range) Processor.                                                                                                 |

| PIC16C6x    | 18- to 40-Pin PICmicro <sup>®</sup> MCU. 14-Bit (Mid-Range) Processor. Optional TMR1<br>& TMR2/Optional SPI/Optional USART/Optional PSP.                        |

| PIC16C62x   | 18-Pin PICmicro <sup>®</sup> MCU. 14-Bit (Mid-Range) Processor. Voltage Comparators<br>Built-In with Voltage Reference/Optional EEPROM Data Memory.             |

| PIC16F62x   | 18-Pin PICmicro® MCU. 14-Bit (Mid-Range) Processor. Flash Program<br>Memory/Voltage Comparators Built-In with Voltage Reference/Internal Reset<br>& Oscillator. |

| PIC16C642   | 28-Pin PICmicro® MCU. 14-Bit (Mid-Range) Processor. Voltage Comparators<br>Built-In with Voltage Reference.                                                     |

| PIC16C662 | 40-Pin PICmicro <sup>®</sup> MCU. 14-Bit (Mid-Range) Processor. Voltage Comparators<br>Built-In with Voltage Reference.                |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| PIC16C71x | 18-Pin PICmicro <sup>®</sup> MCU. 14-Bit (Mid-Range) Processor. 8-Bit ADC.                                                             |

| PIC16C7x  | 18- to 40-Pin PICmicro® MCU. 14-Bit (Mid-Range) Processor. 8-Bit<br>ADC/Optional TMR1 & TMR2/Optional SPI/Optional USART/Optional PSP. |

| PIC16C77x | 28- to 40-Pin PICmicro <sup>®</sup> MCU. 14-Bit (Mid-Range) Processor. 12-Bit<br>ADC/TMR1 & TMR2/USART/I2C/SPI/Optional PSP.           |

| PIC16F8x  | 18-Pin PICmicro <sup>®</sup> MCU. 14-Bit (Mid-Range) Processor. Flash Data and Program Memory.                                         |

| PIC16F87x | 28- to 40-Pin PICmicro <sup>®</sup> MCU. 14-Bit (Mid-Range) Processor. 10-Bit<br>ADC/TMR1 & TMR2/USART/I2C/SPI/Optional PSP.           |

| PIC16C92x | 64-Pin PICmicro <sup>®</sup> MCU. 14-Bit (Mid-Range) Processor. Optional 8-Bit<br>ADC/TMR1 & TMR2/LCD Controller.                      |

| PIC17C4x  | 40-Pin PICmicro <sup>®</sup> MCU. 16-Bit (High-End) Processor. USART/Multiply.                                                         |

| PIC17C5x  | 68-Pin PICmicro <sup>®</sup> MCU. 16-Bit (High-End) Processor. USART/I2C/Multiply/10-Bit ADC.                                          |

| PIC17C6x  | 84-Pin PICmicro <sup>®</sup> MCU. 16-Bit (High-End) Processor.<br>USART/I2C/SPI/Multiply/12-Bit ADC.                                   |

| PIC18Cxxx | 28- to 40-Pin PICmicro <sup>®</sup> MCU. 16-Bit Advanced (18Cxx) Processor.<br>USART/I2C/SPI/10-Bit ADC.                               |

сл

## Mid-range PICmicro® MCU Part Number to Feature Breakout

| Part Number | Comments                                                                                                                   |

|-------------|----------------------------------------------------------------------------------------------------------------------------|

| 16Cx1       | 18-Pin PICmicro <sup>®</sup> MCU. 1K Program Memory. No USART/SPI/I2C.<br>PIC16C61 and PIC16C71 are currently "obsoleted." |

| 16Cx2       | 28-Pin PICmicro <sup>®</sup> MCU. 2K Program Memory. SPI/TMR1 & TMR2.                                                      |

| 16Cx3       | 28-Pin PICmicro <sup>®</sup> MCU. 4K Program Memory. USART/SPI/TMR1 & TMR2.                                                |

| 16Cx4       | 40-Pin PICmicro <sup>®</sup> MCU. 4K Program Memory. USART/SPI/PSP/TMR1 & TMR2.                                            |

| 16Cx5       | 40-Pin PICmicro <sup>®</sup> MCU. 4K Program Memory. USART/SPI/PSP/TMR1 & TMR2.                                            |

| 16Cx6       | 28-Pin PICmicro® MCU. 8K Program Memory. USART/SPI/I2C/TMR1 & TMR2.                                                        |

| 16Cx7       | 40-Pin PICmicro® MCU. 8K Program Memory. USART/SPI/I2C/PSP/TMR1<br>& TMR2.                                                 |

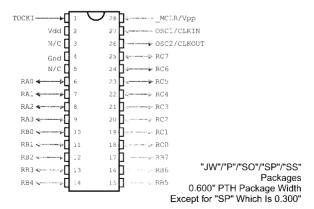

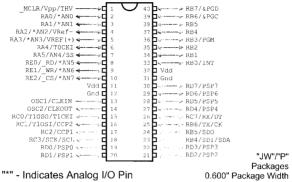

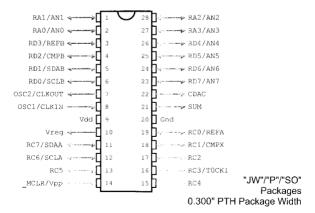

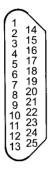

## **Device Pinouts**

As a rule of thumb, Pin-Through-Hole ("PTH") parts ("P" and "JW") are standard 0.300" and 0.600" widths with pins 0.100" apart in dual in-line packages. The height of the device is dependent on the package used. Surface Mount Technology ("SMT") parts are either in dual inline packages ("SO") or in quad plastic chip carriers ("PT", "PQ", and "L").

For actual device dimensions, check the datasheets (on the CD-ROM or from the Microchip Web site) for the PICmicro<sup>®</sup> MCU that you are planning on using. Different packages for different PICmicro<sup>®</sup> MCUs have different via pad and clearance specifications.

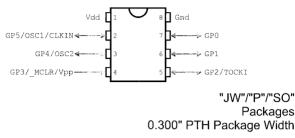

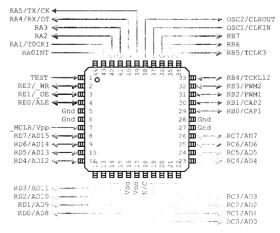

Figure 3.1 "PIC12C508"/"PIC12C509" Pinout

## Low-End

There are no PLCC or QFP packages used for the lowend devices and the pinouts remain the same whether or not the PICmicro<sup>®</sup> MCU is in a surface mount technology or pin-through-hole package (Figs. 3.1–3.4).

"JW"/"P"/"SO" Packages 0.300" PTH Package Width

Figure 3.2 "PIC16C505" Pinout

**Device Pinouts**

9

Figure 3.3 "PIC16C54"/"PIC16C56" Pinout

Figure 3.4 "PIC16C55"/"PIC16C57" Pinout

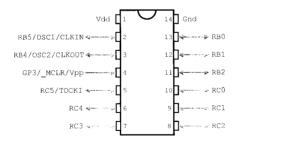

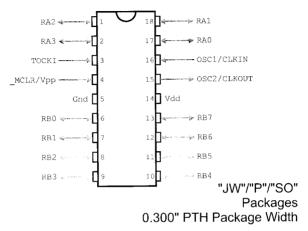

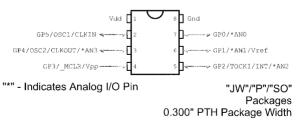

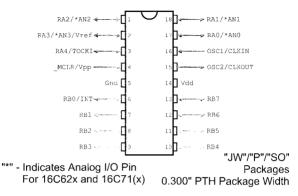

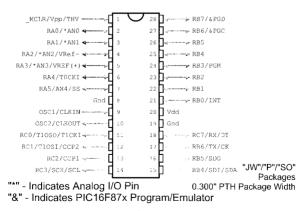

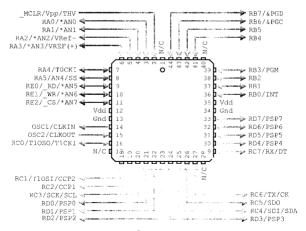

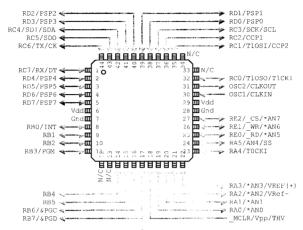

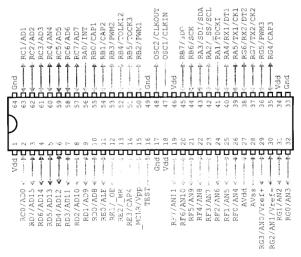

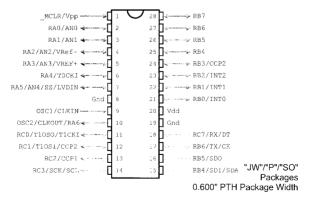

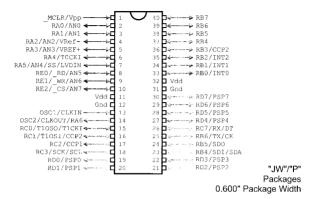

## **Mid-Range**

The mid-range devices have the widest range of pinouts of any of the PICmicro<sup>®</sup> MCU families (Figs. 3.5-3.10). For many of the devices, the pinout is similar, but the pin functions may be different. In these cases, the pins marked with "\*" show that these pins have other, optional purposes. Actual part number functions can be confirmed with Microchip Datasheets.

The PIC14000, which is designed for "Mixed Signals" uses the 28-pin packaging of the standard devices, but the pinouts are different as shown in Fig. 3.11.

The PIC16C92x LCD Driver microcontrollers are fairly high pin count devices. Figure 3.12 shows the 64-pin "DIP" ("Dual In-line Package") part. There is also a "PLCC" and "TQFP" package for the parts as well.

Figure 3.5 "PIC12C67x" Pinout

#### Device Pinouts 11

Figure 3.6 Mid-Range 18-Pin PICmicro® MCU Pinout

Figure 3.7 Mid-Range PICmicro® MCU 28-Pin Device Pinout

"&" - Indicates PIC16F87x Program/Emulator

Figure 3.8 Mid-Range PICmicro® MCU 40-Pin Device Pinout

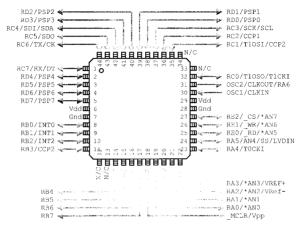

Figure 3.9 Mid-Range PICmicro® MCU 44-Pin "PLCC" Pinout

#### Device Pinouts 13

Figure 3.10 Mid-Range PICmicro® MCU 44-Pin "QFP" Pinout

Figure 3.11 PIC14000 28-Pin Device Pinout

Figure 3.12 PIC16C92x 64-Pin Device Pinout

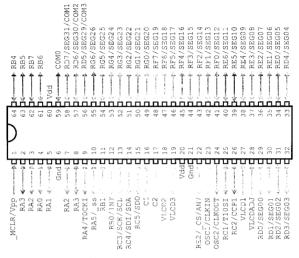

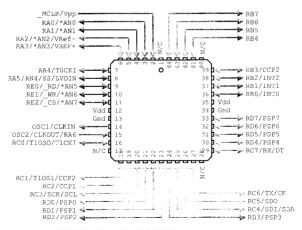

## PIC17Cxx

The PIC17Cxx PICmicro<sup>®</sup> MCUs are available in 40- or 64-pin DIP packages as shown in Figs. 3.13 and 3.14. "PLCC" and "TQFP" surface mount packages as well for the 40-pin parts are displayed in the following graphics (Figs. 3.13–3.16).

0.600" Package Width

"JW"/"P" Packages

Figure 3.13 PIC17C4x 40-Pin Device Pinout

Figure 3.14 PIC17C75x 64-Pin Device Pinout

Figure 3.15 PIC17C4x 44-Pin "PLCC" Pinout

Figure 3.16 PIC17C4x 44-Pin "QFP" Pinout

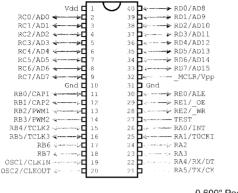

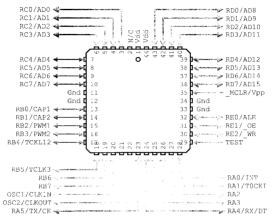

## PIC18Cxx

There is a lot of similarity between the mid-range PICmicro<sup>®</sup> MCU's pinouts and the PIC18Cxx parts, as will be seen in the following pinouts (Figs. 3.17–3.20). Note that several pins that are optional in one PICmicro<sup>®</sup> MCU family are not optional in others.

Figure 3.17 PIC18C2X2 28-Pin Device Pinout

Figure 3.18 PIC18C4X2 40-Pin Device Pinout

Figure 3.19 PIC18C4X2 44-Pin "PLCC" Pinout

#### Device Pinouts 19

Figure 3.20 PIC18C4X2 44-Pin "QFP" Pinout

This page intentionally left blank.

# Chapter

# PICmicro<sup>®</sup> MCU Instruction Sets

Unless otherwise noted, all instructions execute in one instruction cycle.

#### **Parameters**

There are a number of parameters that are used with the instructions. The parameters are defined as:

#### 22 Chapter 4

| Parameter              | Symbol  | Op code<br>letter | Value range                                           |

|------------------------|---------|-------------------|-------------------------------------------------------|

| Don't Care             | N/A     | х                 |                                                       |

| Byte Constant          | k       | k                 | 0 to 0x0FF                                            |

| Register Address       | Reg     | f                 | PICmicro <sup>®</sup> MCU<br>Architecture<br>Specific |

| Destination            | d       | d                 | 0 or 1                                                |

| Selection Bit          | Bit     | b                 | 0 to 7                                                |

| Destination<br>Address | Address | a                 | 0 to 0x07FF                                           |

| Destination Port       | Port    | p                 | PORTA (5) to<br>PORTC(7)                              |

## Low-End Instruction Set

Register Banks are 32 bytes in size in the low-end devices. This makes "Reg" in the range of 0x00 to 0x01F.

| Description                                                          | Instruction  | Operation                                                                          | Op code        |

|----------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------|----------------|

| Add Register Contents to "w"<br>and optionally store result in "w"   | addwf Reg, d |                                                                                    | 0001 11df ffff |

| AND Immediate with "w"                                               | andlw k      | w = w & k<br>Z = (w & k) == 0                                                      | 1110 kkkk kkkk |

| AND Register Contents with "w" and<br>Optionally store result in "w" | andwf Reg, d | if (d == 1)<br>Reg = Reg & w<br>else<br>w = Reg & w<br>endif<br>Z = (Reg & w) == 0 | 0001 01df ffff |

| Clear the Specified Bit<br>in the Register                           | bcf Reg, bit | Reg = Reg &<br>(0x0FF ^<br>(1 << Bit))                                             | 0100 bbbf ffff |

| Description                                                                                                        | Instruction    | Operation                                                  | Op code        |

|--------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------|----------------|

| Set the Specified Bit<br>in the Register                                                                           | bcf Reg, bit   | Reg = Reg  <br>(1 << Bit)                                  | 0101 bbbf ffff |

| Skip if the Specified Bit In the Register is<br>Clear. One Instruction Cycle if Skip not<br>Executed, two if it is | btfsc Reg, bit | if ((Reg &<br>(1 << Bit))) == 0)<br>PC = PC + 1<br>endif   | 0110 bbbf ffff |

| Skip if the Specified Bit In the Register is<br>Set. One Instruction Cycle if Skip not<br>Executed, two if it is   | btfsc Reg, bit | if ((Reg &<br>(1 << Bit))<br>!= 0)<br>PC = PC + 1<br>endif | 0111 bbbf ffff |

| Save the Stack Pointer and jump to the<br>Specified Address (two Instruction<br>cycles)                            | call Address   |                                                            | 1001 aaaa aaaa |

| Clear the Specified Register                                                                                       | clrf Reg       | Reg = 0<br>Z = 1                                           | 0000 011f ffff |

| Clear the "w" Register                                                                                             | clrw           | w = 0<br>Z = 1                                             | 0000 0100 0000 |

| Clear the Watchdog Timer's Counter                                                                                 | clrwdt         | WDT = 0<br>_TO = 1<br>_PD = 1                              | 0000 0000 0100 |

| Complement the Contents of the<br>Specified Register and optionally store<br>the results in "w"                                                                                                             | comf Reg, d   | if $(d == 1)$<br>Reg = Reg ^ 0x0FF<br>else<br>w = Reg ^ 0x0FF<br>endif<br>Z = (Reg ^ 0x0FF)<br>= = 0 | 0010 Oldf ffff |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------|----------------|

| Decrement the Contents of the Register<br>and Optionally store the results in "w"                                                                                                                           | decf Reg, d   | $      if (d == 1) \\ Reg = Reg - 1 \\ else \\ w = Reg - 1 \\ endif \\ Z = (Reg - 1) == 0 $          | 0011 11df ffff |

| Decrement the Contents of the Register<br>and Optionally store the results in "w"<br>and Skip the next instruction<br>if the results are equal to Zero.<br>Two Instruction Cycles taken<br>if Skip Executed | decfsz Reg, d |                                                                                                      | 0010 11df ffff |

| Jump to the Specified Address (two<br>Instruction cycles)                                                                                                                                                   | goto Address  | PC =<br>((STATUS & 0x0E0)<br><< 4) + Address                                                         | 101a aaaa aaaa |

| Description                                                                                                                                                                                                 | Instruction   | Operation                                                                                   | Op code        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------|----------------|

| Increment the Contents of the Register<br>and Optionally store the results in "w"                                                                                                                           | incf Reg, d   | $      if (d == 1) \\ Reg = Reg + 1 \\ else \\ w = Reg + 1 \\ endif \\ Z = (Reg + 1) == 0 $ | 0010 10df ffff |

| Increment the Contents of the<br>Register and Optionally store the<br>results in "w" and Skip the next<br>instruction if the results are equal to<br>Zero. Two Instruction Cycles<br>taken if Skip Executed | incfsz Reg, d |                                                                                             | 0011 11df ffff |

| OR Immediate with "w"                                                                                                                                                                                       | iorlw k       |                                                                                             | 1101 kkkk kkkk |

| OR Register Contents with "w" and<br>Optionally store result in "w"                                                                                                                                         | iorwf Reg, d  | if (d == 1)<br>Reg = Reg   w<br>else<br>w = Reg   w<br>endif<br>Z = (Reg   w) == 0          | 0001 00df ffff |

| Check Register Contents equal<br>to zero and Optionally store<br>result in "w"                                                                   | movf Reg, d | if (d == 0)<br>w = Reg<br>endif<br>Z = Reg == 0 | 0010 00df ffff |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------|----------------|

| Load "w" with an Immediate value                                                                                                                 | movlw k     | $\mathbf{w} = \mathbf{k}$                       | 1100 kkkk kkkk |

| Store the value in "w"                                                                                                                           | movwf Reg   | Reg = w                                         | 0000 001f ffff |

| Waste one Instruction                                                                                                                            | nop         |                                                 | 0000 0000 0000 |

| Move the contents of "w" into the<br>OPTION Register                                                                                             | option      | TRIS(Port) = w                                  | 0000 0000 0010 |

| Resume Execution after Subroutine<br>and Place a constant value in<br>"w" (Two Cycles used)                                                      | retlw k     | $    w = k \\ SP = SP - 1 \\ PC = [SP] $        | 1000 kkkk kkkk |

| Resume Execution after Subroutine<br>and Place Zero in "w" (Two Cycles<br>used). This is actually a "retlw 0"<br>instruction that MPLAB provides | return      | w = 0<br>SP = SP - 1<br>PC = [SP]               | 1000 0000 0000 |

| Description                                                                      | Instruction | Operation                                                                                                                                                       | Op code        |

|----------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Rotate the Register left through carry<br>and optionally Save the Result in "w"  | rlf Reg, d  | $\begin{array}{l} Temp = C \\ C = (Reg >> 7) \& 1 \\ if (d == 1) \\ Reg = (Reg << 1) \\ + Temp \\ else \\ w = (Reg << 1) \\ + Temp \\ endif \end{array}$        | 0011 01df ffff |

| Rotate the Register right through carry<br>and optionally Save the Result in "w" | rrf Reg, d  | $\begin{array}{l} Temp = C \\ C = Reg \& 1 \\ if (d == 1) \\ Reg = (Reg >> 1) \\ + (Temp << 7) \\ else \\ w = (Reg >> 1) \\ + (Temp << 7) \\ endif \end{array}$ | 0011 00df ffff |

| Go into "Standby" Mode (Indeterminate<br>number of cycles used)                  | sleep       | _TO = 1<br>_PD = 0                                                                                                                                              | 0000 0000 0011 |

| Subtract "w" Register Contents from<br>Register and Optionally store<br>Result in "w"   | subwf Reg, d | 0000 lodf ffff |

|-----------------------------------------------------------------------------------------|--------------|----------------|

| Swap the Upper and lower nybbles<br>of a Register and Optionally store<br>result in "w" | swapf Reg, d | 0011 10df ffff |

| Description                                                                 | Instruction  | Operation                                                                                   | Op code        |

|-----------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------|----------------|

| Move the contents of "w" into the<br>Tri-state control Register of the Port | tris Port    | TRIS(Port) = w                                                                              | qqq0 0000 0000 |

| XOR Immediate with "w"                                                      | xorlw k      |                                                                                             | 1111 kkkk kkkk |

| XOR Register Contents with<br>"w" and Optionally store result in "w"        | xorwf Reg, d | $      if (d == 1) \\ Reg = Reg ^ w \\ else \\ w = Reg ^ w \\ endif \\ Z = (Reg ^ w) == 0 $ | 0001 10df ffff |

### **Mid-Range Instruction Set**

Register Banks are 128-bytes in size in the low-end devices. This makes "Reg" in the range of 0 to 0x07F.

| Description                                                              | Instruction  | Operation                     | Op code           |

|--------------------------------------------------------------------------|--------------|-------------------------------|-------------------|

| Add Immediate to "w"                                                     | addlw k      |                               | ll lllx kkkk kkkk |

| Add Register<br>Contents to "w"<br>and optionally<br>store result in "w" | addwf Reg, d |                               | 00 0111 dfff ffff |

| AND Immediate<br>with "w"                                                | andlw k      | w = w & k<br>Z = (w & k) == 0 | 11 1001 kkkk kkkk |

| Description                                                                                                                         | Instruction    | Operation                                                                          | Op code           |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------|-------------------|

| AND Register<br>Contents with<br>"w" and Optionally<br>store result in "w"                                                          | andwf Reg, d   | if (d == 1)<br>Reg = Reg & w<br>else<br>w = Reg & w<br>endif<br>Z = (Reg & w) == 0 | 00 0101 dfff ffff |

| Clear the Specified<br>Bit in the Register                                                                                          | bcf Reg, bit   | Reg = Reg &<br>(0x0FF ^<br>(1 << Bit))                                             | 01 00bb bfff ffff |

| Set the Specified<br>Bit in the Register                                                                                            | bcf Reg, bit   | Reg = Reg  <br>(1 << Bit)                                                          | 01 01bb bfff ffff |

| Skip if the Specified<br>Bit in the<br>Register is Clear.<br>One Instruction Cycle<br>if Skip not Executed,<br>two if Skip Executed | btfsc Reg, bit | if ((Reg &<br>(1 << Bit))) == 0)<br>PC = PC + 1<br>endif                           | 01 10bb bfff ffff |

| Skip if the Specified<br>Bit in the Register<br>is Set. One Instruction<br>Cycle if Skip not<br>Executed, two if it is | btfsc Reg, bit | if ((Reg &<br>(1 << Bit))<br>!= 0)<br>PC = PC + 1<br>endif                                                                   | 01 11bb bfff ffff |

|------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Save the Stack Pointer<br>and jump to the Specified<br>Address (two<br>Instruction cycles)                             | call Address   | $      [SP] = PC \\ SP = SP + 1 \\ PC = ((PCLATH << 8) \\ & 0x01800) + \\ Address $                                          | 10 0aaa aaaa aaaa |

| Clear the Specified Register                                                                                           | clrf Reg       | Reg = 0<br>Z = 1                                                                                                             | 00 0001 1fff ffff |

| Clear the "w" Register                                                                                                 | clrw           | w = 0<br>Z = 1                                                                                                               | 00 0001 0xxx xxxx |

| Clear the Watchdog<br>Timer's Counter                                                                                  | clrwdt         | WDT = 0<br>_TO = 1<br>_PD = 1                                                                                                | 00 0000 0110 0100 |

| Complement the Contents<br>of the Specified Register<br>and Optionally store<br>the results in "w"                     | comf Reg, d    | $      if (d == 1)       Reg = Reg ^ 0x0FF       else       w = Reg ^ 0x0FF       endif       Z = (Reg ^ 0x0FF)       == 0 $ | 00 1001 dfff ffff |

| Description                                                                                                                                                                                                       | Instruction   | Operation                                                                                                                                                                                                                                               | Op code           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Decrement the Contents<br>of the Register and<br>Optionally store the<br>results in "w'                                                                                                                           | decf Reg, d   | if (d == 1)<br>Reg = Reg - 1<br>else<br>w = Reg - 1<br>endif<br>Z = (Reg - 1) == 0                                                                                                                                                                      | 00 0011 dfff ffff |

| Decrement the Contents<br>of the Register and<br>Optionally store the<br>results in "w" and Skip<br>the next instruction if the<br>results are equal to Zero.<br>Two Instruction Cycles<br>taken if skip executed | decfsz Reg, d | $\label{eq:constraint} \begin{array}{l} \text{if } (d==1) \\ \text{Reg} = \text{Reg} - 1 \\ \text{else} \\ \text{w} = \text{Reg} - 1 \\ \text{endif} \\ \\ \text{if } ((\text{Reg} - 1) == 0) \\ \text{PC} = \text{PC} + 1 \\ \text{endif} \end{array}$ | 00 1011 dfff ffff |

| Jump to the Specified<br>Address (two Instruction<br>cycles)                                                                                                                                                      | goto Address  | PC =<br>((PCLATH << 8)<br>& 0x01800) +<br>Address                                                                                                                                                                                                       | 10 laaa aaaa aaaa |

| Increment the Contents<br>of the Register and<br>Optionally store the<br>results in "w"                                                                                                                           | incf Reg, d   | $      if (d == 1) \\ Reg = Reg + 1 \\ else \\ w = Reg + 1 \\ endif \\ Z = (Reg + 1) == 0 $                                                                                                                                                             | 00 1010 dfff ffff |

| Increment the Contents<br>of the Register and<br>Optionally store the<br>results in "w" and Skip<br>the next instruction if<br>the results are equal to<br>Zero. Two Instruction Cycles<br>taken if Skip Executed | incfsz Reg, d | if $(d == 1)$<br>Reg = Reg + 1<br>else<br>w = Reg + 1<br>endif<br>if $((Reg + 1) == 0)$<br>PC = PC + 1<br>endif | 00 1111 dfff ffff |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------|-------------------|

| OR Immediate with "w"                                                                                                                                                                                             | iorlw k       |                                                                                                                 | 11 1000 kkkk kkkk |

| OR Register Contents<br>with "w" and Optionally<br>store result in "w"                                                                                                                                            | iorwf Reg, d  | if (d == 1)<br>Reg = Reg   w<br>else<br>w = Reg   w<br>endif<br>Z = (Reg   w) == 0                              | 00 0100 dfff ffff |

| Check Register Contents<br>equal to zero and<br>Optionally store Register<br>contents in "w"                                                                                                                      | movf Reg, d   | if (d == 0)<br>w = Reg<br>endif<br>Z = Reg == 0                                                                 | 00 1000 dfff ffff |

| Description                      | Inst |

|----------------------------------|------|

| Load "w" with an immediate value | mov  |

| Description                                                                                            | Instruction | Operation                           | Op code           |

|--------------------------------------------------------------------------------------------------------|-------------|-------------------------------------|-------------------|

| Load "w" with an immediate value                                                                       | movlw k     | w = k                               | 11 00xx kkkk kkkk |

| Store the value In "w"                                                                                 | movwf Reg   | Reg = w                             | 00 0000 lfff ffff |

| Waste one Instruction                                                                                  | nop         |                                     | 00 0000 0xx0 0000 |

| Move the contents of<br>"w" into the OPTION<br>Register. Use of this instruction<br>is not recommended | option      | TRIS(Port) = w                      | 00 0000 0110 0010 |

| Resume Execution after<br>Interrupt (Two Cycles used)                                                  | retfie      | GIE = 1<br>SP = SP - 1<br>PC = [SP] | 00 0000 0000 1001 |

| Resume Execution after<br>Subroutine and Place a<br>constant Value in "w"<br>(Two Cycles used)         | retlw k     | w = k  SP = SP - 1  PC = [SP]       | 11 01xx kkkk kkkk |

| Resume Execute after<br>Subroutine (Two Cycles<br>used)                                | return     | SP = SP - 1<br>PC = [SP]                                                                                                                                        | 00 0000 0000 1000 |

|----------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Rotate the Register left<br>through carry and<br>Optionally Save the<br>Result in "w"  | rlf Reg, d | $\begin{array}{l} Temp = C \\ C = (Reg >> 7) \& 1 \\ if (d == 1) \\ Reg = (Reg << 1) \\ + Temp \\ else \\ w = (Reg << 1) \\ + Temp \\ endif \end{array}$        | 00 1101 dfff ffff |

| Rotate the Register right<br>through carry and<br>Optionally Save the<br>Result in "w" | rrf Reg, d | $\begin{array}{l} Temp = C \\ C = Reg \& 1 \\ if (d == 1) \\ Reg = (Reg >> 1) \\ + (Temp << 7) \\ else \\ w = (Reg >> 1) \\ + (Temp << 7) \\ endif \end{array}$ | 00 1100 dfff ffff |

| Go into "Standby" Mode<br>(Indeterminate number of<br>cycles used)                     | sleep      | _TO = 1<br>_PD = 0                                                                                                                                              | 00 0000 0110 0011 |

| Description                                                                           | Instruction  | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Op code           |

|---------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Subtract "w" Contents from<br>Immediate and Store the<br>Result In "w"                | sublw k      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11 110x kkkk kkkk |

| Subtract "w" Register Contents<br>from Register and Optionally<br>store Result in "w" | subwf Reg, d | $      if (d == 1) \\ Reg = Reg + \\ (w ^ 0x0FF) + 1 \\ else \\ w = Reg + \\ (w ^ 0x0FF) + 1 \\ endif \\ C = (Reg + \\ (w ^ 0x0FF) + 1) \\ > 0x0FF \\ Z = ((Reg + \\ (w ^ 0x0FF) + 1) \\ & 0x0FF) = 0 \\ DC = ((Reg & 0x0F) \\ + ((w ^ 0x0FF) \\ & & 0x0FF) \\ & & 0x0FF) \\ & & & 0x0FF) \\ & & & & 0x0FF) \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & & \\ & & & & \\ & & & & & \\ & & & & & \\ & & & & \\ & & & & & \\ &$ | 00 0010 dfff ffff |

| Swap the Upper and lower<br>Nybbles of a Register<br>and Optionally store<br>result in "w"                                       | swapf Reg, d | if $(d == 1)$<br>Reg =<br>((Reg & 0x0F0)<br>>>4) +<br>((Reg & 0x00F)<br><<4)<br>else<br>w = $((Reg \& 0x0F0)$<br>>>4) +<br>((Reg & 0x00F)<br><<4)<br>endif | 00 1110 dfff ffff |

|----------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Move the contents of "w"<br>into the Tri-state control<br>Register of the Port. Use<br>of this Instruction is not<br>recommended | tris Port    | TRIS(Port) = w                                                                                                                                             | 00 0000 0110 0ppp |

| XOR Immediate with "w"                                                                                                           | xorlw k      |                                                                                                                                                            | 11 1010 kkkk kkkk |

| XOR Register Contents with<br>"w" and Optionally store<br>result in "w"                                                          | xorwf Reg, d | $      if (d == 1) \\ Reg = Reg ^ w \\ else \\ w = Reg ^ w \\ endif \\ Z = (Reg ^ w) == 0 $                                                                | 00 0110 dfff ffff |

# **PIC17Cxx Instruction Set**

The PIC17Cxx's instruction set is very similar to both the low-end and the mid-range instruction sets except for the basic "move" instructions. These instructions are quite a bit different because of the operation of the PIC17Cxx's "primary" register subset of the total 256 possible addresses.

| Instruction                                                       | Format         | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit pattern         |

|-------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Add a Constant to the<br>"wreg" and store the<br>Result in "wreg" | addlw Constant | $\label{eq:second} \begin{array}{l} \text{wreg} = \text{wreg} \\ + \text{Constant} \\ \text{if} \left( \left( \left( \text{wreg} > 0 \right) \\ \& \left( \text{Constant} > 0 \right) \right) \\ \& \left( \left( \text{wreg} \\ + \text{Constant} > 0 \text{VOFF} \right) \\ OV = 1 \\ else \\ OV = 0 \\ \text{if} \left( \text{wreg} + \\ \text{Constant} \right) > 0 \text{vOFF} \\ C = 1 \\ else \\ C = 0 \\ \text{if} \left( \left( \text{wreg} & \text{A 0xOF} \right) + \\ (\text{Constant} & \text{A 0xOF} \right) \\ DC = 1 \\ else \\ DC = 0 \\ \text{if} \left( \left( \text{wreg} + \\ \text{Constant} \right) & \text{A 0xOFF} \right) \\ = 0 \text{ x0OF} \\ DC = 1 \\ else \\ DC = 0 \\ \text{if} \left( \left( \text{wreg} + \\ \text{Constant} \right) & \text{A 0xOFF} \right) \\ = 0 \text{ x0OO} \\ Z = 1 \\ else \\ Z = 0 \end{array}$ | 1011 0001 kkkk kkkk |

| Instruction                                                                                         | Format       | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit pattern         |

|-----------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Add "wreg" to the Contents<br>of "Reg" and store the<br>Result According to "d"<br>Result in "wreg" | addwf Reg, d | $\label{eq:constraints} \begin{array}{l} \mbox{if } ("d" = = 1) \\ \mbox{wreg} = \mbox{wreg} \\ \ + \ Reg \\ \mbox{else} \\ \ Reg = \mbox{wreg} \\ \ + \ Reg \\ \ if (((wreg > 0)) \\ \& ((Reg > 0)) \\ \& ((Reg > 0)) \\ \& ((wreg \\ + \ Reg) \\ \ > 0 x07F)) \\ \ OV = 1 \\ \mbox{else} \\ \ OV = 0 \\ \mbox{if } ((wreg + \ Reg) > 0 x07F)) \\ \ C = 1 \\ \mbox{else} \\ \ C = 0 \\ \mbox{if } ((wreg \& 0x0F) + \ (Reg \& 0x0F) + \ (Reg \& 0x0F)) \\ \ > 0x0F) \\ \ DC = 1 \\ \mbox{else} \\ \ DC = 0 \\ \end{array}$ | 0000 111d ffff ffff |

|                                                                                                          |               | if (((wreg +<br>Reg) & 0x0FF)<br>= = 0x000)<br>Z = 1<br>else<br>Z = 0                                                                                                                                                                                                                                                                                                                       |                     |

|----------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Add "wreg" to the Contents<br>of "Reg" and "C", store the<br>Result According to "d"<br>Result in "wreg" | addwfc Reg, d | $      if ("d" == 1) \\ wreg = wreg \\ + Reg + C \\ else \\ Reg = wreg \\ + Reg + C \\ if (((wreg > 0) \\ & ((wreg > 0)) \\ & ((wreg + Reg + C) \\ > 0x07F)) \\ OV = 1 \\ else \\ OV = 0 \\ if ((wreg + Reg + C) > 0x0FF) \\ C = 1 \\ else \\ C = 0 \\ if (((wreg & 0x0F) + (Reg & 0x0F) + (Reg & 0x0F) + C) \\ > 0x0F) \\ DC = 1 \\            DC = 1 \\                                 $ | 0001 000d ffff ffff |

| •  |

|----|

| ÷- |

| -  |

| _  |

| Instruction                                                                                         | Format         | Operation                                                                                                            | Bit pattern         |

|-----------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------|---------------------|

|                                                                                                     |                | else<br>DC = 0<br>if (((wreg +<br>Reg + C) & 0x0FF)<br>= 0x000)<br>Z = 1<br>else<br>Z = 0                            |                     |

| AND a Constant to the<br>"wreg" and store the<br>Result in "wreg"                                   | andlw Constant | wreg = wreg<br>& Constant<br>if ((wreg &<br>Constant)<br>= = 0x000)<br>Z = 1<br>else<br>Z = 0                        | 1011 0101 kkkk kkkk |

| AND "wreg" to the Contents<br>of "Reg" and store the<br>Result According to "d"<br>Result in "wreg" | andwf Reg, d   | if ("d" == 1) $wreg = wreg$ $& Reg$ $else$ $Reg = wreg$ $& Reg$ $if ((wreg & Reg)$ $= 0x000)$ $Z = 1$ $else$ $Z = 0$ | 0000 101d ffff ffff |

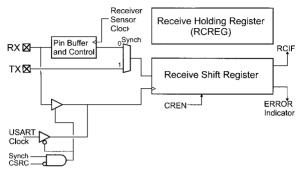

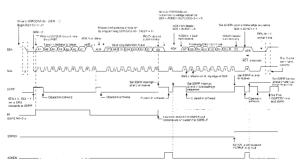

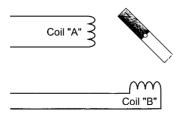

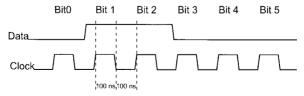

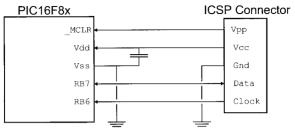

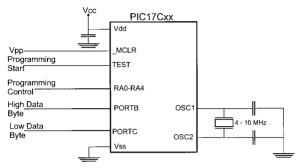

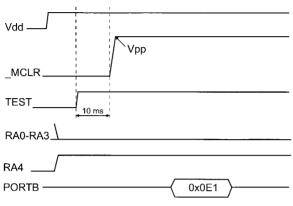

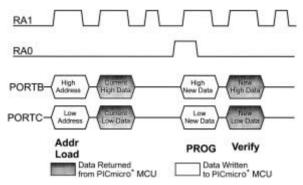

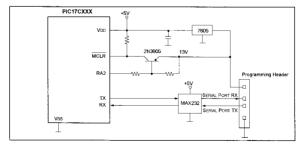

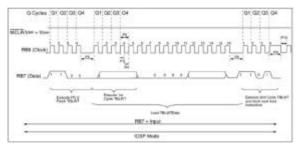

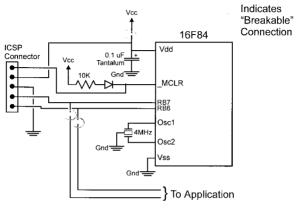

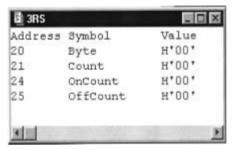

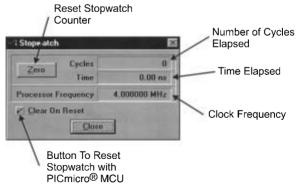

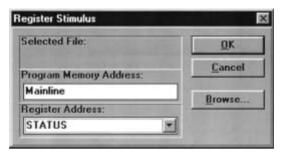

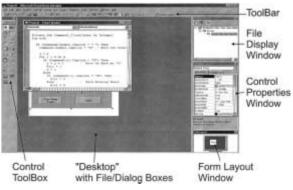

| Clear the Specified Bit<br>in "Reg"                                                                                             | bcf Reg, Bit   | Reg = Reg<br>& (0x0FF ^<br>(1 << Bit))                                                    | 1000 lbbb ffff ffff |