## High input impedance c.m.o.s. amplifier

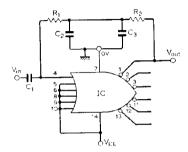

### Circuit description

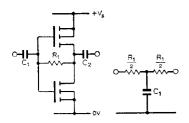

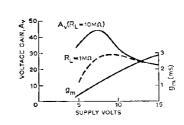

C.m.o.s. circuits have been designed for digital systems. Basic building block is the inverter consisting of a complementary pair of enhancement-mode m.o.s. devices with threshold voltages in the region of 1.7V and peak current capabilities of a few tens of milliamperes at maximum forward bias. Input resistance is extremely large with the leakage currents of the protection diodes as the limiting action. The individual device  $g_m$  is around 1 to 2mS for forward gate-source voltages in excess of 5V. Biased in the linear mode, the devices each have  $|V_{gs}| \approx V_s/2$ , so maximum forward bias is  $\approx 7.5$ V for the rated supply voltage of 15V. This restricts the upper value of  $g_m$  that can be attained. In the absence of an external load resistance the voltage gain is limited by the finite slope resistance. An unusual property of this circuit is that the voltage gain falls

with increasing supply voltage, as the relatively small rise in  $g_m$  is more than offset by the fall in output slope resistance at the higher resulting currents. The disadvantage of operating at low supply voltages (and hence currents) is that the voltage gain is more load-dependent and the upper cut-off frequency falls sharply. To maximize the input resistance while using d.c. negative feedback to stabilize the operating point, the feedback resistor is decoupled to ground. Gate current is negligible and the input and output quiescent voltages are equal.

Other c.m.o.s. devices using different technologies, e.g. silicon gate, ion implantation, offer greater bandwidths and/or lower threshold voltages. Complementary m.o.s. circuits designed for the linear market have been recently announced.

Component changes

IC<sub>1</sub>: Any c.m.o.s. inverter including CD4001 NOR gate, CD4009/CD4049 inverting buffers, MC1407, MC14009 and other equivalents.

$R_1$ : 220k to 22M $\Omega$ .

$C_1$ : Sets the lower frequency at which the negative feedback becomes operative, reducing the input impedances. 0.1 to 10uF (time constant  $R_1C/2$ ).

$C_2$ : Depends on load which, with this circuit, cannot be very low unless transconductance properties alone required with little voltage gain. 0.1 to  $100\mu$ F.

$V_{\rm s}$ : 3 to 15V. At voltages below 5V the quiescent current becomes very small and output impedance is very high.

### Circuit modifications

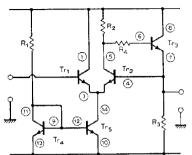

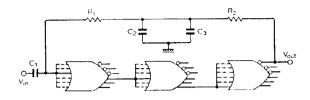

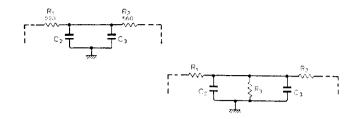

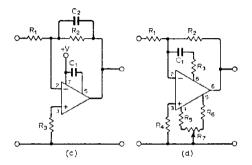

• Negative feedback may be applied over any odd number of inverting stages, e.g. over three as in the circuit shown left. Multiple phase shifts within the amplifier, together with the high voltage gain available, make the method difficult to apply without precautions. Open-loop gains of 80dB and greater may occur. Even decoupling the feedback still allows oscillation at low frequencies via the coupling/decoupling/supply time-constants.

- A better method of controlling gain than simply attenuating it is to cascade stages with shunt and series negative feedback as shown centre where inserting a resistor in the source of each device in stage 1 reduces and defines the transconductance. Shunt feedback across stage 2 defines its transresistance and the combination has a lower but well-defined voltage gain.

- Because the above amplifier is non-inverting, d.c. feedback may be applied via the third stage used purely as a d.c. coupling element linking A-A', B-B', with the overall a.c. feedback decoupled.

### Further reading

RCA, COS/MOS Digital Integrated Circuits, 1973, pp.24-30, pp.37-42, p.346, p.355.

Wujek, J. H. Field-effect transistor circuits, in Electronic Circuits Manual by J. Markus, McGraw-Hill 1971, p.22. Ferranti Ltd, FET Source Follower and Bootstrapped FET Source Follower, FETs and Applications, no. 22, 1965.

#### Cross references

Series 12, cards 4 & 7 Series 11, cards 5 & 6

### Shunt-peaked wideband amplifier

### Circuit data/

0.2in dia.)

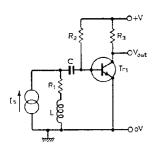

Supply: +6V, 4.5mA Tr<sub>1</sub>:  $1/5 \times CA3046$ C:  $10\mu F$  tantalum R<sub>1</sub>:  $68\Omega$ ; R<sub>2</sub>:  $100k\Omega$ R<sub>3</sub>:  $680\Omega$ L:  $1.83\mu H$  (38 turns 28 swg, close wound on

### Circuit description

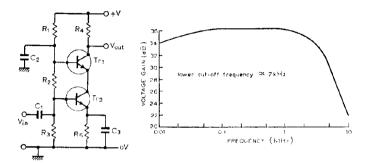

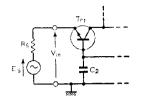

Bandwidth of a common-emitter amplifier may be extended by including an inductor in shunt with its input producing a shunt-peaked amplifier. The circuit is fed from a current source, or alternatively in a cascaded amplifier R<sub>1</sub> and L may be used as the collector coupling network of each stage which is loaded by the input impedance of the following transistor.

Because the gain-bandwidth product of a transistor varies with its collector current,  $R_2$  was chosen to maximize the gain-bandwidth product for the device used. Resistor  $R_3$  was chosen to make  $V_{\rm CE} \approx + V/2$  and  $R_1$  to provide the desired low-frequency current gain. Source resistance was  $100\Omega$ , so a current source was simulated by a chain of ten 1-k $\Omega$  resistors in series to reduce the effect of the shunt capacitance of a single 10-k $\Omega$  resistor on the measured high-frequency response.

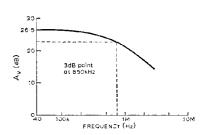

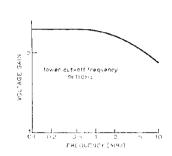

With L=0, amplifier input voltage falls with increasing frequency due to transistor input (and Miller effect) capacitance. With L in circuit, low-frequency response is the same but a low-Q resonance occurs between L and  $C_{\rm in}$  of the transistor, causing the response to peak as the frequency is raised towards its original cut-off value.

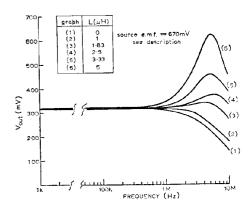

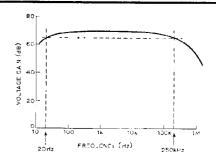

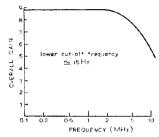

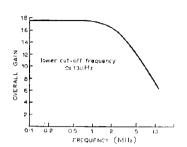

By designing L on the basis of available transistor parameter data and the required current gain, it is possible to produce a maximally-flat gain response while maximizing stage gain-bandwidth product. Alternatively, a good starting point is to use the measured low frequency input resistance and upper cut-off frequency with L=0 to estimate  $C_{in}$  and then design L to resonate with this value in the region of the desired cut-off frequency with the peaked response. (See curve 3 above.)

Component changes

Useful range of supply +3 to +30V. Values of  $R_2$  and  $R_3$  should be adjusted to produce  $f_T$  max. for transistor if maximum stage gain-bandwidth product is to be achieved. Select  $R_1$  to give desired low-frequency gain, and C to give desired lower cut-off frequency. High-frequency response may be tailored to suit requirements by choice of L value. (See curves 2, 4, 5 & 6.)

### Circuit modifications

• Up to five cascaded stages may be obtained with the same integrated circuit package but it may prove easier to obtain the desired response experimentally than by calculated design. Problems of alignment and possible instability due to interaction between cascaded shunt-peaked stages can be alleviated if each transistor feeds a resistive load. The load on each device consists of L and  $R_1$  in parallel with the input impedance of the following stage, as shown left. Load impedance may be made purely resistive by adjusting the values of  $R_1$  and L to be  $r_{\rm bb}f(r_{\rm bb}'+R_{\rm in})/R_{\rm in}$  and  $C_{\rm in}r_{\rm bb}'^2$  respectively, where  $r_{\rm bb}'$  the transistor base spreading resistance. In such a constant-resistance cascade, L and  $R_1$  cannot be used to adjust the gain and bandwidth of the amplifier which must be trimmed by adjusting the collector currents of the transistors.

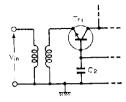

- A series-peaking inductor may be connected between a low-impedance source and the base, as shown centre, to extend the bandwidth. Stage gain-bandwidth product is less than for the shunt-peaked arrangement and its maximum value cannot be achieved with a maximally flat response.

- Another high-frequency compensation network, widely used in pulse applications, is shown right. Bandwidth may be extended by making  $R_1C_1-R_{\rm in}C_{\rm in}$  but the stage gain-bandwidth product, while constant, does not approach that of the shunt-peaked stage. However the constancy of the gain-bandwidth product does allow exchange of gain for bandwidth by adjusting  $R_1$ .

### Further reading

Cahausi, M. S. Electronic Circuits, Van Nostrand, 1971, chapter 4.

Shea, R. F. (Ed.), Amplifier Handbook, McGraw-Hill 1966, section 25.4.2.

Joyce, M. V. & Clarke, K. K. Transistor Circuit Analysis, Advision-Wesley, 1963, chapter 8.

Markus, J. Electronic Circuits Manual, McGraw-Hill, 1971, p.913.

### Cross references

Series 12, cards 5, 9 & 12. Series 7, card 9

## High-gain wideband amplifier

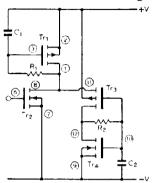

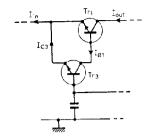

### Circuit description

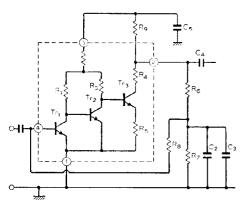

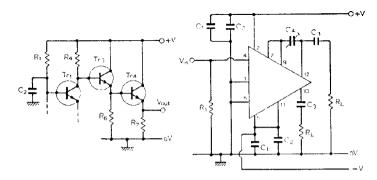

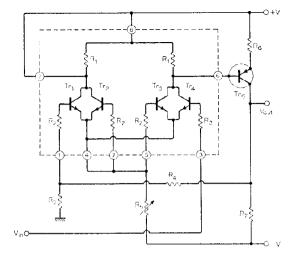

This amplifier uses an integrated circuit developed for consumer applications. It is simple in design, consisting of three commonemitter transistors directly coupled so that the collector potentials of  $Tr_1$ ,  $Tr_2$  are defined by the base potentials of  $Tr_2$ ,  $Tr_3$  respectively, i.e. they are at  $\approx 0.6$ V. Resistor  $R_5$  has a low value with only a marginal effect on these potentials. Output potential is forced by the feedback effect via  $R_6$ ,  $R_7$ ,  $R_8$  to be some defined multiple of the base potential of  $Tr_1$ . If  $R_8 < R_8$ ,  $R_7$  then the output p.d. to ground is  $\approx (R_6/R_7+1)V_{\text{be}1}$  and would typically be set near the supply mid-value. Current in each stage increases with increasing supply voltage, and as a result both open-loop gain and bandwidth increase. In-

creased current also reduces the input impedance. Resistor R<sub>9</sub> determines quiescent output current provided output voltage has been fixed by feedback as outlined above. As there are three stages all contributing phase shift, the total phase-shift is in excess of 180° before the magnitude of the gain falls towards unity. Hence it is difficult to apply heavy negative feedback to extend the bandwidth at the expense of gain as can be done with amplifiers single common-emitter stages. (For audio frequency applications it is possible to control the feedback to produce defined characteristics as for tape recording/playback amplifiers.) As the high gain extends to high frequencies,  $A_{\rm v} \approx 100$  at  $f-4{\rm MHz}$ , proper grounding, decoupling and use of short leads, screened where appropriate are all important.

### Component changes

IC: No direct replacements but groups of three transistors from CA3046 and similar multi-transistor packages may be used.

$R_6$ ,  $R_7$ : Ratio fixes output quiescent voltage  $\approx (R_6/R_7+1)0.6V$ . Resistors may be increased to minimize loading on output, but base current of  $Tr_1$  becomes significant factor in determining quiescent conditions. Typical range 5k to  $50k\Omega$ .

$\hat{R}_s$ : Also limited by base current effects, but may be increased up to  $10k\Omega$  to maximize input resistance of circuit if required.  $R_s$ : Determines output stage quiescent current and hence maximum load current. No advantage to making too high since current in preceding stages fixed by internal resistors. 2.2k to  $22k\Omega$ .

$+V_s$ : 2 to 18V. At low voltages, gain falls sharply. Choose  $R_s$ ,  $R_7$  in conjunction with  $V_s$  to bias output near mid-point of supply for maximum output swing.

$C_1$ ,  $C_3$ ,  $C_4$ : Determine low frequency cut off. Maintain ratio increasing values for pro rata fall in cut-off.  $C_4$  may be reduced greatly if feeding high impedance load.

### Circuit modifications

• Any group of three transistors may be used in similar configurations. Simple arrangement shown for low-voltage applications where output quiescent voltage of 0.6V would be adequate. Again decoupling of feedback essential since gain/

phase properties too complex for application of heavy negative feedback. Resistors  $R_1$  to  $R_5$  may be comparable value resistors (1k to  $10k\Omega$ ) though  $R_4$ ,  $R_5$  may be higher if somewhat higher output direct voltage desired.

- $\bullet$  By using complementary transistors, each transistor has current defined by  $V_{be}$  of succeeding stage. This makes current and hence gain/bandwidth less dependent on supply voltage. Complementary versions of each form are equally possible, reversing the supply voltage.

- The good high frequency gain allows its use in 10.7 MHz i.f. applications with the d.c. feedback being applied via the input tuned circuit and the output taken to a ceramic filter. Similar principles apply at 470 kHz but the high voltage gain makes careful design obligatory. In all r.f. applications drive from a  $50\Omega$  source is normal, but the output impedance of the circuit is relatively high.

### Further reading

Motorola Linear Integrated Circuits Data Book, 2nd edition 1972, pp.7-561 to 7-564.

CA3095E Wideband Amplifier, RCA Databook SSD-201A, 1973, p.249.

#### Cross references

Series 12, cards 5, 10 & 11.

## Series 12: Wideband amplifiers—4

## Wideband voltage followers

### Circuit data

IC: LM310  $R_1$ :  $1k\Omega$   $R_2$ ,  $R_3$ :  $100k\Omega$   $R_4$ :  $3.3k\Omega$  $C_1$ :  $2.2\mu$ F

$C_2$ : 0.01 $\mu$ F Supply: +15V

### Circuit description

A specially-designed monolithic voltage-follower, the 310 has a combination of highly desirable parameters: high input impedance, low output impedance, and wide frequency range. The negative feedback is connected internally but some modifications to performance that can be made externally include offset zero by means of  $R_1$ , increased output current capability by preloading with  $R_4$  at the expense of increased dissipation, and a.c. coupling to source, bootstrapping the bias resistors  $R_2$ ,  $R_3$  to minimize loading effects.

Slew-rate limitations imposed by the maximum charging rate of an internal compensation capacitor, mean that the large signal bandwidth is much less than small signal bandwidth—true of amplifiers having heavy negative feedback in general.

### Performance

Upper cut-off frequency for small signals.

15MHz for zero source resistance, 2MHz for  $10k\Omega$ . At 1MHz, output impedance is  $25\Omega$ , output voltage swing is  $\pm 3V$ , and input impedance is 3pF plus strays.

### Component changes

IC: Direct replacements from many manufacturers. Any op-amp compensated for 100% negative feedback may be used. In general it will not be possible to achieve the same spread of parameters, i.e. high input impedance may preclude wide bandwidth.

$R_2$ ,  $R_3$ : Increase for higher  $Z_{1n}$  at expense of increased offset.  $C_2$ ,  $C_1$ : Determine lower cut-off frequency (with  $R_1$ ,  $R_3$ ). Combination gives inductive term to input impedance at low frequencies. 0.1 to  $10\mu F$ .

$R_4$ : Increases negative current capability at expense of dissipation.

V:  $\pm 5$  to  $\pm 15$ V (down to  $\pm 3$ V in extreme cases).

### Further reading

LM110—An Improved IC Voltage Follower, National Semiconductor Linear Applications Handbook, 1972, p.LB11-1 and 2.

Campbell, T. C. Application note ICAN-5213, in RCA Databook SSD-202, 1972, pp.203-4.

Markus, J. Electronic Circuits Manual, McGraw-Hill p.13.

### Cross references

Series 12, cards 1 & 11. Series 7, card 3.

#### Circuit data

$Tr_{1-5}$ : CA3046  $R_2$ : 3.9k $\Omega$   $R_1$ : 4.7k $\Omega$   $R_3$ : 1k $\Omega$   $R_4$ : 1k $\Omega$ Supply:  $\pm 2.5V$

· P

### Circuit description

Using the five transistors in an i.e. package (CA3046), this is a simple wide-band voltage follower. A similar circuit could be used with discrete transistors replacing current mirror  $Tr_4$ ,  $Tr_5$  by a similar current source or by a single resistor particularly if the supply voltages were higher. Transistors  $Tr_1$ ,  $Tr_2$  are the differential pair comparing input with output, the use of a monolithic pair giving good temperature drift. Transistor  $Tr_3$  is an emitter follower within the feedback loop. Resistor R<sub>4</sub> may be required to suppress very high frequency oscillations (dependent on circuit layout). Not shown, but generally important, is the decoupling of the supply voltages as close to the i.c. as possible—typically 0.01 to  $1\mu F$ .

### Performance

Upper cut-off frequency  $\approx 4.5 \text{MHz}$ Output impedance  $\approx 10\Omega$ Input impedance:  $\approx 100 \text{k}\Omega$ Output voltage swing  $\approx 2.5 \text{V pk-pk}$  at 100 kHz

### Circuit modifications

- Replace  $Tr_4$ ,  $Tr_5$  by any other constant current source (or even resistor, with reduced stability against supply changes).

- Increase open-loop gain output capability, by replacing R<sub>0</sub>, R<sub>0</sub> with constant current sources.

- Replace Tr<sub>3</sub> by common emitter p-n-p transistor taking signal from Tr<sub>1</sub> collector instead. Higher open-loop gain, greater output swing capability, greater likelihood of oscillations requiring compensating capacitor, e.g. collector-base of Tr<sub>3</sub>.

### Component changes

IC: CA3546, CA3045, CA3586.

$R_1$ :  $1k\Omega$  to  $100k\Omega$ . Lower values increase bandwidth and dissipation.

$R_2$ : Set to carry half current in  $R_1$  (assuming unity ratio for current mirror). Typically  $R_1 \approx R_2$ .

$R_s$ : Low values maximize output swing and dissipation 330 $\Omega$  to 33k $\Omega$ .

V:  $\pm 2$  to  $\pm 7\frac{1}{2}V$ . Higher voltages possible if discrete transistors used.

## Series 12: Wideband amplifiers—5

## Bipolar cascode wideband amplifier

Circuit description

The bipolar transistor cascode amplifier offers very good isolation between its input and output ports, so that the possibility of instability is virtually non-existent for all types of load. Input transistor  $Tr_2$  acts as a common-emitter stage which is loaded by the upper transistor connected in the common-base configuration and having a very low input impedance. Thus the common-emitter stage has a current gain approaching  $h_{re}$  and the voltage swing at its collector is very small, producing a significant reduction of the internal feedback between collector and base. Bandwidth of the common-emitter stage approaches  $f_{\beta}$  and as that of the common-base stage is much larger, the complete circuit behaves like a common-emitter amplifier as far as voltage gain and current gain are concerned, but has a wider bandwidth than is achiev-

Circuit data

Supply: +6V, 1.2mA

Tr<sub>1</sub>, Tr<sub>2</sub>:  $1/5 \times CA3046$ R<sub>1</sub>:  $39k\Omega$ ; R<sub>2</sub>:  $3.3k\Omega$   $R_3$ : 33k $\Omega$ ;  $R_4$ : 2.2k $\Omega$

$R_5$ :  $1k\Omega$

$C_1$ ,  $C_2$ ,  $C_3$ :  $1\mu F$  $V_{in}$ : 10mV r.m.s.

able with a simple common-emitter stage providing the same high voltage gain.

A reasonable estimate of the 3-dB bandwidth obtainable with the cascode amplifier may be made using available data and the relationship: gain-bandwidth product  $(f_T) \approx h_{fe} \cdot f_{\beta}$  if it is assumed that  $h_{fe}$  and  $f_{\beta}$  are the approximate current gain and bandwidth values for the whole circuit. Each of the transistors in the integrated circuit array has typical  $h_{fe}$  and  $f_T$  values of 110 and 450MHz respectively, with  $I_C \approx 1.2$ mA giving  $f_{\beta} \approx 4.1$ MHz. (Measured upper 3dB cut-off frequency was approximately 3.7MHz for the circuit.)

### Component changes

Useful range of supply +2 to  $\pm 30$ V.

$V_{\rm in}({\rm max}) \approx 40 \,{\rm mV}({\rm pk-pk}).$

Midband gain falls by 3dB when output is loaded with approximately  $6.8k\Omega$  (capacitively coupled).

Upper cut-off frequency largely determined by R<sub>4</sub> for given transistors.

Lower cut-off frequency adjustable by changing  $C_1$ ,  $C_2$  and  $C_3$ . Tr<sub>1</sub> and Tr<sub>2</sub> may each be replaced by  $\frac{1}{4} \times CA3018$  or equivalent discrete devices e.g. 2N706-type.

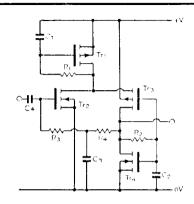

### Circuit modifications

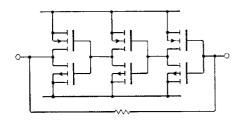

- One of the differentially-connected pair of transistors in the CA3046 package may be connected as an output emitter-follower stage to provide a low output impedance cascode amplifier. If a CA3018 package is used, all four transistors may be used by following the cascode with a pair of cascaded emitter followers as shown left. In this form, with  $R_6$ =3.3k $\Omega$  and  $R_7$ =2.7k $\Omega$  a voltage gain of about 36dB is obtainable with an upper cut-off frequency of approximately 11MHz.

- A pair of cascode stages with a common tail resistor may be used as a differential cascode amplifier. This arrangement is the basis of the CA3040 integrated circuit wideband amplifier, which employs high-input-impedance emitter-follower buffer stages between the input terminals and the common-emitter sections of the cascodes. Outputs from the cascode common-base stages are fed to the output terminals via emitter followers to produce a reasonably low output impedance.

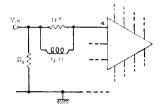

- Centre circuit shows the CA3040 connected to a pair of

equal load resistors (R<sub>L</sub>) which receive antiphase outputs. With the amplifier connected to a 50- $\Omega$  source and  $R_{\rm L}=50\Omega$  the voltage gain to each output is about 22dB with a bandwidth of approximately 30MHz. The values increase to about 32dB and 50MHz respectively when R<sub>L</sub> is raised to 1k $\Omega$  and the bandwidth may be increased to about 90MHz by including the input series peaking circuit shown right. Supplies must be decoupled with capacitors C<sub>1</sub> and C<sub>2</sub> at the integrated-circuit package pins and ferrite beads on the supply leads and careful printed circuit layout are necessary. Supply  $\pm 6$ V, R<sub>1</sub> 50 $\Omega$ , C<sub>1</sub>, C<sub>3</sub> 100nF, C<sub>2</sub> 1nF, C<sub>4</sub> is a small trimmer to adjust high-frequency gain and phase balance.

### Further reading

Theriault, G. E. et al. Application of the RCA-CA3018 Integrated-Circuit Transistor Array, RCA Databook SSD-202 1972, pp.68-70.

Austin, W. M. Principal Features and Applications of the RCA-CA3040 Integrated-Circuit Wideband Amplifier, RCA Databook SSD-202, 1972, pp.171-81.

Ghausi, M. S. Electronic Circuits, Van Nostrand, 1971, pp.271-3.

### Cross references

Series 12, cards 2, 3, 7 & 12. Series 7, card 5.

## Series 12: Wideband amplifiers—6

### Wideband amplifier using e.c.l.

Circuit description

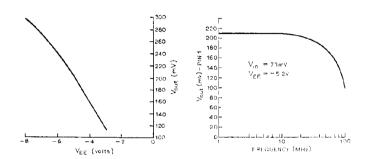

The integrated circuit is an emitter-coupled logic gate designed for high-speed digital applications. This type of gate has an input stage consisting of a long-tailed pair with multiple inputs to one half of the pair via separate transistors having their collector-emitter paths in parallel. Each half of this differential stage feeds an emitter follower output stage, a number of which may be paralleled within the package. Thus, at least one inverted and at least one non-inverted output is available and the logic gate may be used as a linear, wideband amplifier provided it is correctly biased, for example by means of R<sub>1</sub> and R<sub>2</sub> as shown above. This simple arrangement of connecting one of the logical NOR outputs back to the input provides self-biasing of the gate that ensures that the d.c. input and output voltages are the same except for the small drop

across  $R_1$  and  $R_2$ . This is only possible if the gate is operating in the middle of its transfer characteristic, the arrangement automatically compensating for changes in bias and offset voltages.

Only the d.c. component of the output signal is fed back to the input,  $C_2$  and  $C_3$  decoupling the a.c. component. Capacitor  $C_1$  prevents any d.c. component of the input signal from disturbing the self-biasing conditions. The a.c. signal voltage available at the NOR output being used to derive the feedback, is typically 3 to 4% lower than that obtainable from other NOR outputs is approximately 9 to 10%, higher than at the unloaded NOR outputs.

Careful printed circuit layout is required if a smooth, high-frequency roll-off is to be obtained in the frequency response.

Useful range of  $V_{EE} \approx -3$  to -8V (see graph).

Minimum load resistance for 10% fall in mid-band gain  $\approx$  270 $\Omega$  (a.c. coupled via 100nF capacitor).

Distortion is less than 1% for  $V_{\rm in}$  in the range approximately 1 to 20mV and useful  $V_{\rm in}$  (max) without significant distortion is approximately 200mV pk-pk.

For bandwidths in excess of 300MHz use MC1660.

### Circuit modifications

- More than one input of the gate may be used to increase gain by connecting others in parallel, but the offset voltage between output and input rises as the number of paralleled inputs increases. This may not be a severe disadvantage in certain applications.

- The simple self-biasing arrangement may be applied over several e.c.l.-gate amplifying stages, as shown left.

- A given total bias network resistance  $(R_1+R_2)$  may be decoupled asymmetrically. For example, if it is required that the bias-network loading of the output be reduced without changing  $(R_1+R_2)$ , values such as those shown centre may be used. This will cause the input impedance of the amplifier to fall from about  $390\Omega$  to about  $220\Omega$ .

• The biasing arrangement may be changed to allow an increase in both the input and output impedances without changing the d.c. input and output voltages. One such arrangement is shown right, where the junction of  $R_1$  and  $R_2$  may be returned to the 0-volt rail through as uitable-value, additional bias resistor  $R_3$ . For example, with  $R_1$ ,  $R_2$  2.2k $\Omega$ , a suitable value for  $R_3$  would be around 47k $\Omega$ . This arrangement slightly increases voltage gain.

### Further reading

Using e.c.l. gates as wideband amplifiers, *Electronic Engineering*, June 1973.

MECL Integrated Circuits Data Book, Motorola, 2nd edition, 1972, pp.5-3 to 5-6 and pp.4-17 to 4-20.

#### Cross references

Series 11, card 7. Series 12, cards 8 & 10.

© 1974 IPC Business Press Ltd.

## Series 12: Wideband amplifiers—7

### FET cascode amplifiers

Circuit data

Supply:  $\pm 7.5$ V

IC: CD4007AE  $R_1$ ,  $R_2$ :  $1M\Omega$   $C_1$ :  $0.1\mu$ F;  $C_2$ :  $0.33\mu$ F

Voltage gain:  $\approx 26$ Cut-off frequency: 320kHz

Alternative bias for single supply:  $R_3$ ,  $R_4$ :  $1M\Omega$

$C_3$ :  $1\mu F$ ;  $C_4$ :  $0.01\mu F$

### Circuit description

The basic principle of a cascode stage is that of a commonemitter or common-source amplifier feeding directly into a common-base or common-gate stage, so that the first stage feeds into a near short-circuit. This allows it to develop its maximum current gain or transconductance, but more important the voltage swing at the collector or drain is small. Large voltage swings produce relatively large currents in the inevitable feedback capacitance, with a corresponding heavy shunting effect at high frequencies. This reduction in feedback (commonly called the Miller effect though first discussed by Blumlein) is of particular importance in wideband and r.f. amplifiers. In particular, the better the isolation between input and output the higher the gain that can be achieved

consistent with stability. The devices need not be in series for d.c. purposes though this is more common. In the circuit shown, based on a low-cost c.m.o.s. i.c.,  $Tr_2$  is a common-source stage whose output signal current is diverted into  $Tr_3$  provided that  $Tr_1$  has a high dynamic impedance at a.c. (see circuit modifications). The voltage gain of the cascode pair is equal to or greater than the highest voltage gain obtainable from a single stage, while coupling between output and input is minimized.

An alternative version is shown in which a decoupled d.c. feedback path via  $R_s$ ,  $R_4$  gives self-biasing (with a.c.-coupled source). The high input resistance of the m.o.s. devices together with the possibility of operation at  $V_{\rm dg}=0$  allows for simple biasing networks and offsets the disadvantage of the wider tolerance on m.o.s. devices as against bipolar transistors.

Component changes

IC: Equivalents of CD4007AE including MC14007, etc. Other combinations of enhancement-mode m.o.s.f.e.ts may function but simpler circuits can be devised for these. This circuit was intended to make best use of this low-cost i.c.

Supply voltage: Positive voltage may need to be increased with some devices; negative rail is then reduced accordingly to stay within rating.

$R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$ : Not critical.  $100k\Omega$  to  $22M\Omega$ . With low resistances, low-frequency time constants are raised unless large capacitances used, while input impedance falls for second version. Very high resistances bring noise/hum/leakage problems.

$C_1$ ,  $C_2$ ,  $C_3$ ,  $C_4$ : High values to improve low-frequency response if required.

### Circuit modifications

• The high impedance of the circuit is possible because the p-channel enhancement-mode m.o.s.f.e.t. can still have the drain well beyond the knee of its characteristics if biased with drain and gate at equal quiescent potentials. Provided the a.c. applied to the drain is adequately decoupled by  $R_1C_1$ , the dynamic impedance approaches that of the drain-source ( $R_1$  may be very large and still achieve correct bias). The current mirror approach retains the high dynamic resistance down to d.c. at the expense of a second m.o.s.f.e.t.

- Cascode circuits may have the devices in series, sharing the same d.c. current (rather than in parallel as with the complementary stage above). If the input device is a junction f.e.t., the simplest circuits demand only a bipolar transistor with base potential set to a value in excess of the pinch-voltage of the f.e.t. to achieve good cascode performances. The f.e.t. determines the input performance including very high input impedance at low frequencies, while the cascode configuration extends the high impedance to higher frequencies while allowing higher overall gain.

- All f.e.t. circuits are equally possible provided  $Tr_2$  has a higher  $V_D$  than  $Tr_1$ . Transistor  $Tr_3$  is a source follower to isolate the load  $R_2$  from stray and load capacitances, i.e. increasing bandwidth of output circuit.

### Further reading

FET Circuit Applications, National Semiconductor Linear Applications Handbook, 1972, p.AN32-2.

Schade, O. H. Jr. Application note ICAN-6080, in RCA Data Book SSD-203A, 1973, pp.299-300.

### Cross references

Series 12, cards 1 & 5, series 11, cards 5 & 6. Series 7, card 5.

## Series 12: Wideband amplifiers—8

### Wideband amplifiers with t.t.l., r.t.l., d.t.l.

### Circuit data

Supply: 5V, 19mA IC: 1/4×SN7400

$C_1$ :  $10\mu$ F tantalum  $R_1$ :  $220\Omega$ ;  $R_2$ :  $560\Omega$   $V_{in}$ : 50mV r.m.s.

### T.t.l. gate description

Without the use of negative feedback, the normal transfer characteristic of the t.t.l. gate is designed to provide well-defined logic levels with a high-gain transition region between them causing the gate normally rest in either the on or off condition. Compared with the static on or off state, the supply current drain increases sharply as the gate is switched through the narrow transition region. Although designed for medium-speed digital switching applications a t.t.l. NAND gate can be converted into a linear wideband amplifier. By addition of  $R_1$  and  $R_2$ , as shown, the shunt-derived shunt-applied negative feedback has the effect of linearizing the overall d.c. transfer characteristic, eliminating the well-defined logic states, widening the transition region, reducing the gain, and increasing the standing supply current.

Thus, a suitable operating point may be established, with a quiescent supply current of about 19mA, which will allow

linear amplification of input signals having levels up to about 800mV pk-pk in the frequency range of approximately 100Hz to 12MHz. Unused gate inputs may be paralleled with the used input rather than being left open-circuit. Alternatively, a logic signal may be applied to the unused input to provide a gating facility on the used input's signal.

### Component changes

Useful range of supply +3 to +5.5V.

Changing  $R_2$  varies gain, shape of the transfer characteristic, and signal-handling capability.

In principle, all four gates in the package may be used simultaneously for linear amplification but the package dissipation is then far in excess of that when used for logic operation.

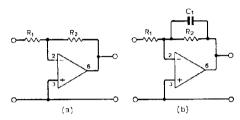

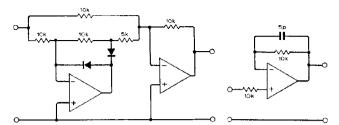

**R.t.l.** and d.t.l. gate descriptions. A dual NAND/NOR r.t.l. gate, contained in a single 914 package (shown dotted), has  $Tr_1$ ,  $Tr_2$  and  $Tr_3$ ,  $Tr_4$  connected as a long-tailed pair with  $R_5$  returned to the -V rail and serving as an approximation to a constant-current source (left). Transistor  $Tr_5$  is used as an inverting output stage having a gain of two, with the output at its collector fed back to  $Tr_1$  via  $R_4$  and  $R_3$ . Thus, a non-inverted output is available for signals applied to  $Tr_4$  base. The d.c. output voltage can be set to zero with the input grounded, by adjusting  $R_5$ . A gain of 10 with bandwidth greater than 10MHz is obtainable with a supply of  $\pm 6V$ ,  $Tr_5$  2N3702,  $R_1$  640 $\Omega$ ,  $R_2$  450 $\Omega$  (internal to 914),  $R_3$ ,  $R_5$ ,  $R_6$ ,  $Ik\Omega$ ,  $R_4$  10k $\Omega$ ,  $R_7$  2.2k $\Omega$ .

• Circuit right shows a d.t.l. buffer gate connected in the collector circuit of  $Tr_1$  using the former's  $\div V$  and extender pins. The gate is operated at its logic switching threshold where it provides high gain. Negative feedback is provided by  $R_2$  and  $R_3$  which determine the overall gain. By decoupling a section of  $R_2$ , the gain may be increased without affecting the d.c. operating conditions. A gain of 10, a bandwidth in excess of 500kHz and a load-driving capability of 1 volt into  $300\Omega$  is achievable with a supply of +5V,  $IC \frac{1}{2} \times 932$ ,  $Tr_1 2N2222$ ,  $R_1 120k\Omega$ ,  $R_2 120\Omega$ ,  $R_3 1.1k\Omega$ ,  $C_1 10nF$ ,  $C_2 100pF$ , and  $C_3 10\mu F$ .

### Further reading

Kolataj, J. H. Linearize your t.t.l. gates—then build useful circuits with them, in 400 Ideas for Design, Hayden 1971, pp.2-3.

Klipstein, D. L. Build an operational amplifier from a dual NAND/NOR gate, in 400 Ideas for Design, Hayden 1971, p.21.

Jones, D. Wideband amplifier uses a single d.t.l. gate, in 400 Ideas for Design, Hayden 1971, p.23.

## Amplifiers using d.c. feedback pair

### Circuit data

Supply: +5V, 6mA  $Tr_1$ ,  $Tr_2$ :  $1/5 \times CA3046$   $C_1$ :  $10\mu F$  tantalum  $R_1$ :  $3.9k\Omega$ ;  $R_2$ :  $10k\Omega$

$R_3$ :  $150\Omega$

$V_{C_1}$ : 1.5V;  $V_{B_1}$ : 0.67V

$V_{E_2}$ : 0.77V

Source e.m.f.: 50mV r.m.s.

Circuit description

Transistor Tr<sub>1</sub> is connected in the common-emitter configuration and feeds the emitter follower Tr, with overall shuntderived shunt-applied feedback via R2, which allows the overall gain and input impedance to be adjusted. If the circuit is supplied from an ideal voltage source the gain will be high and the bandwidth relatively small. Such a source could be heavily loaded when connected directly to the circuit shown above. This is due to the equivalent load on the source of hie of Tr<sub>1</sub> in parallel with  $R_2/(1+|A_v|)$ , where  $|A_v| \approx g_m R_{L_1}$ ;  $R_{L_1}$ being the equivalent load resistance seen by Tr<sub>1</sub>. The signal generator available had an output resistance of  $100\Omega$  which approximately matched the input resistance of the amplifier. This can be seen to be reasonable assuming hie of Tr<sub>1</sub> to be approximately 2.5k $\Omega$  and  $|A_v| \approx 80$  with  $R_{L_1} \approx 3k\Omega$ . To define the overall gain and input impedance and to provide a wider bandwidth a resistor may be included in series with C<sub>1</sub>. Response shown applies with a 900- $\Omega$  resistance included and

the overall gain  $= V_{\rm out}/\text{source e.m.f.}$  If it is desired to match the amplifier input resistance to a defined source resistance, this can be achieved using the circuit as shown above and adjusting the value of  $R_{\circ}$ .

The integrated-circuit package used contains a five-transistor array, two connected as a long-tailed pair. One of the single transistors has its emitter connected to the integrated circuit substrate which must be connected to the most negative supply rail, hence this transistor can be conveniently used as  $Tr_1$  and any other as  $Tr_2$ . A discrete component version of the circuit is also viable.

### Component changes

Useful range of  $V_{ee} \approx +3$  to +15V.

Maximum source e.m.f. 72mV r.m.s. with  $V_{ce} = +5\text{V.}$   $R_2$  adjustable to provide desired overall gain, bandwidth of input impedance e.g. with  $R_2 = 47k\Omega$  and circuit as shown

above: overall gain  $\approx 22$  and bandwidth  $\approx 3.4$ MHz.

Resistance values may be scaled by a given factor, e.g. increasing values by factor of 10: overall gain  $\approx 28$  and bandwidth  $\approx 1 \text{MHz}$ .

### Circuit description

Another amplifier based on the configuration shown over, and also using an integrated-circuit transistor array is shown above. Transistors are contained in a single CA3018 package with Tr<sub>2</sub> emitter and Tr<sub>3</sub> base internally connected. The circuit arrangement of Tr<sub>1</sub>, Tr<sub>2</sub> serving as a common-emitter common-collector pair followed by Tr<sub>3</sub>, Tr<sub>4</sub> in the same configuration is designed to reduce internal capacitive feedback. The Tr<sub>2</sub>-emitter follower acts as a low output impedance source to drive the Tr<sub>3</sub> common-emitter stage and also provides a low-capacitance high-impedance loading on the Tr<sub>1</sub> common-emitter stage.

All stages are d.c. coupled with two negative feedback paths. Feedback from  $Tr_2$  emitter to  $Tr_1$  base is effective at d.c. and low frequencies while that from  $Tr_3$  collector to  $Tr_1$  collector functions at all frequencies. Feedback provides stability of d.c. operating conditions and allows a gain-bandwidth tradeoff to be made. When supplied from a 50- $\Omega$  source, a voltage gain of 49dB with a bandwidth of approximately 32MHz is obtainable with a supply of +6V,  $C_1$ ,  $C_2$

$1\mu$ F,  $C_3$  470nF,  $R_1$  3.5k $\Omega$ ,  $R_2$  8.2k $\Omega$   $R_3$  22k $\Omega$ ,  $R_4$  18k $\Omega$ ,  $R_5$  1.8k $\Omega$ ,  $R_6$  2.5k $\Omega$   $R_7$  1k $\Omega$ ,  $R_8$  2.7k $\Omega$ , using input signals in the range  $7\mu$ V to 4mV (r.m.s.). Lower cut-off frequency largely depends on the capacitors used and is about 800Hz with the above values.

### Further reading

RCA Application note ICAN 5296, in Databook SSD-202, 1972, pp.68/9.

Cherry, E. M. and Hooper, D. E. Design of wide-band transistor feedback amplifiers, *Proc.I.E.E.*, vol. 110, 1963, pp.375-87.

Tuil, J. Transistor-equipped aerial amplifiers—wideband amplifiers, *Electronic Applications*, vol. 28, 1968, pp.75-8.

### Cross references

Series 12, cards 2, 8 & 12.

Series 7, card 9

Series 4, card 4.

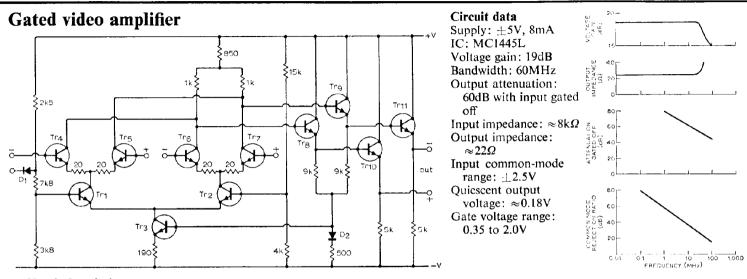

### Circuit description

The long-tailed pair is the key to the operation of this circuit, as of so many linear i.cs. The  $V_{\rm be}/I_{\rm C}$  characteristic of a bipolar transistor is given by  $I_{\rm C}=I_{\rm S}$  exp  $(qV_{\rm be}/kT)$ . Transconductance is obtained by differentiating  $I_{\rm C}$  with respect to  $V_{\rm be}$ , and is found to be proportional to  $I_{\rm C}$ . Thus controlling  $I_{\rm C}$  gives proportional control of the voltage gain of an amplifier provided that the collector load is low enough to allow the full transconductance to be developed. Used with a single transistor an output signal may be gated on and off by such a

means, but the shift in d.c. level carries the gate signal through into the output circuit. With long-tailed pairs as shown,  $Tr_3$  sustains a constant total current using common-mode feedback via the emitters of  $Tr_8$ ,  $Tr_9$ . If  $Tr_3$  conduction increases the collector potentials of  $Tr_4$ ,  $Tr_6$  must fall regardless of which the current is channelled through. This fall in potential at each collector is coupled via the emitter followers  $Tr_8$ ,  $Tr_9$  to close the d.c. feedback loop and stabilize operating conditions. The base of  $Tr_2$  is fixed while that of  $Tr_1$  is normally more positive,

ensuring that  $Tr_4$ ,  $Tr_5$  are the conducting transistors, i.e. having sufficient  $g_m$  to give an overall voltage gain of 18 to 20dB. Transistor  $Tr_2$  has negligible current and  $Tr_6$ ,  $Tr_7$  contribute nothing to the output.

If the potential at the base of  $Tr_1$  is lowered, either by placing a low direct voltage at the gate input  $(D_1)$ , or by taking the input to the negative supply rail through a resistor, then the currents in  $Tr_6$ ,  $Tr_7$  increase at the expense of  $Tr_4$ ,  $Tr_5$ . Hence the signals applied to these differential inputs are gated by a d.c. input. This input may be changed rapidly to allow gating for very short durations or may have intermediate values that allow the inputs to be summed in varying proportions.

### Component changes

IC: MC1445, 1545; similar i.cs with different bias arrangements include Silicon General SG1402/2402/3402. "Discrete" versions based on transistor arrays are also possible but no particular advantages would be expected except possibility of operating at unusual supply voltage/current levels. Balanced modulators/demodulators (MC1496) have similar input stages with free collectors suitable for coupling into tuned circuits.

If the frequency range is more limited, it is possible to adapt analogue multipliers with one input switched between zero and some finite value. This also allows reversal of phase of the output if the control input polarity is reversed.

$V_s$ :  $\pm 3.5$  to  $\pm 12V$ .  $R_L$ : At low supply voltages the output quiescent current may be increased by placing external resistors in parallel with the  $5.0k\Omega$  internal resistors. This increases the signal current that may be capacitively coupled into a load, while lowering the output impedance. 10k to  $1k\Omega$  at  $\pm 5V$  supply. Observe maximum dissipation limits of device (dependent on package,

ambient temperature, but up to 400mW at <50°C).

### Circuit modifications

- By applying the mean value of the output to a standard op-amp, the output can be made to provide a sensitive error signal for departures of the mean i.e. output potential from ground. If the op-amp is operated from a higher positive voltage than that required by the wide-band i.e., then d.e. feedback ensures that the positive voltage applied to the i.e. forces the mean output close to zero (depending on the op-amp offset of a few millivolts). This allows d.e. coupling of signal from input to output of wide-band amplifier with negligible offset.

- For single-ended supplies the unused inputs are taken to a decoupled potential divider, with the option of a  $50\Omega$  resistance added to define the input impedance of any signal input, e.g. capacitively coupled as shown. The gate terminal then becomes compatible with a t.t.l., c.m.o.s. logic gate sharing a common ground line.

### Further reading

Welling, B. and Russell, R. Using the MC1545: Monolithic Gated Video Amplifier, Application note AN-475, Motorola 1969.

Cross references Series 12, cards 3 & 6.

## High-speed operational amplifiers

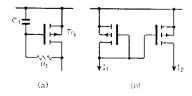

$R_1$ ,  $R_2$ :  $10k\Omega$ Slew rate:  $80V/\mu s$ Small-signal bandwidth 14MHz  $R_1$ :  $5k\Omega$ ,  $R_2$ :  $10k\Omega$   $C_1$ : 5pFVoltage gain: -2Comparable figures to (a)

### Circuit description

The bandwidth available from operational amplifiers has been extended by many manufacturers to the level where they can be applied to problems previously requiring specially-designed wideband amplifiers. The circuits shown use a monolithic i.c. the LM318, showing how manufacturers are able to provide compensation points to modify the high-frequency characteristics—trading in stability margins for increased slew rates, minimum settling times, etc. The internal structure of any particular i.c. at this level of performance is immensely complex and most users will have to treat them as black boxes.

R<sub>1</sub>, R<sub>2</sub>:  $10k\Omega$ , R<sub>3</sub>:  $5k\Omega$ C<sub>1</sub>:  $0.1\mu$ F, C<sub>2</sub>: 5pFShortens settling time to  $1\mu$ s for 0.1% accuracy after 10V step  $R_1$ ,  $R_2$ :  $4.7k\Omega$   $R_3$ :  $3.3k\Omega$ ,  $R_4$ :  $1k\Omega$   $R_5$ ,  $R_6$ :  $27k\Omega$ ,  $R_7$ :  $2.5k\Omega$ Slew rate:  $150V/\mu s$

Using hybrid techniques as well as discrete circuitry, amplifiers are available with slew rates in excess of  $1000V/\mu s$  and bandwidths greater than 100MHz. Methods of construction are more costly than monolithic circuits and they are relevant to specialized applications. In general to achieve such very high bandwidths, the open-loop voltage gain has to be restricted to the range 1 to 5000, while the monolithic amplifier above is optimized for best bandwidth consistent with voltage gains > 100,000.

### Circuit description

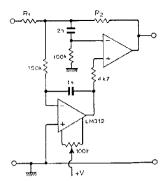

• As a standard operational amplifier, circuits commonly used with 741, 301 and similar devices may be adapted to high frequency units such as the LM318. Layout and decoupling are important, but high frequency amplifiers, oscillators, filters and the like follow similar configurations, generally with comparable resistance values and reduced capacitances. To combine the wide frequency range with high input resistance the technique shown may be adopted. At very low frequencies the high input impedance amplifier-LM312 or similar—develops its full gain applying its inverted output to the non-inverting input of the high-frequency amplifier. The overall characteristic is inverting and the feedback is negative, while the minimal input current of the high-impedance unit permits R<sub>1</sub> and R<sub>2</sub> to have megohm values. At high-frequencies the integrator configuration of the LM312 leaves the noninverting input of the LM318 virtually grounded. The signal appears on the inverting input via the CR network and the feedback remains negative. The two time constants define the

cross-over regions the overall gain being sustained to1MHz.

- Non-linear circuits may be extended to higher frequencies, and for example precision half- and full-wave rectifiers operate to an order of magnitude higher in frequency than with 741, etc. At these higher frequencies, Schottky diodes with their smaller forward voltage drop and absence of charge storage are worthwhile alternatives to even high-speed conventional diodes.

- Component values for the voltage follower mode are similar to those for the unity-gain inverter. Not all amplifiers are compensated for 100% feedback, but may be optimized for higher gains instead.

### Further reading

LM318 data sheet, National Semiconductor Linear Integrated Circuits Databook, 1972, pp.185-9.

Young, R. L. Lift i.c. op-amp performance, *Electronic Design*, vol 4, no. 21, 15 Feb, 1973, pp.66-9.

Motorola application note—AN276, 14MHz wideband amplifier using the MC1530 op-amp.

### Cross references

Series 12, cards 3 & 4.

## Common-base wideband amplifier

Circuit description

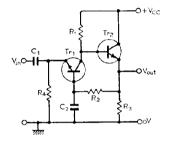

The input stage consists of  $Tr_1$  in the common-base configuration with this transistor feeding  $Tr_2$  acting as an emitter follower with overall shunt-derived shunt-applied feedback through  $R_2$ . This arrangement is similar to the circuit shown on card 9, except that the source feeds the emitter instead of the base of  $Tr_1$ , indicating that the d.c. feedback pair is a convenient method of biasing a common-base stage.

Capacitor  $C_1$  prevents any d.c. component present in the input signal from affecting the biasing, or it may be thought of as necessary if the source cannot sink current from  $Tr_1$  emitter. Capacitor  $C_2$  grounds the base of  $Tr_1$  to a.c. signals. The input impedence of the circuit is low and may be adjusted or matched to a source, by means of  $R_1$  which controls the collector current and hence the emitter current of  $Tr_1$ . This type of circuit is useful for applications where the common-

### Circuit data

Supply: +5V, 8mA  $Tr_1$ ,  $Tr_2$ :  $1/5 \times CA3046$   $C_1$ ,  $C_2$ :  $10\mu F$  tantalum  $R_1$ :  $3.9k\Omega$ ;  $R_2$ :  $10k\Omega$   $R_3$ :  $150\Omega$ ;  $R_4$ :  $470\Omega$ Source e.m.f.:

30mV r.m.s.

Source res.:  $100\Omega$

base configuration offers advantages such as small non-linearity of its transfer characteristic and relatively constant gain with frequency, while providing moderate gain due to the impedance transformation between input and output.

The integrated circuit used is the same as that for card 9 where one transistor has its emitter connected to the substrate which must be connected to the most negative supply rail (0V in this case). Because neither  $Tr_1$  nor  $Tr_2$  has its emitter grounded in the above circuit the substrate-connected transistor cannot be used but its emitter must still be grounded.

### Component changes

Useful range of  $V_{ce}$ : +3 to +15V.

Maximum source e.m.f.  $\approx 37 \text{mV r.m.s.}$  (with  $V_{ee} = +5 \text{ V}$ ).

With other resistors in the same ratios R<sub>1</sub> may be:

- (a) raised as high as  $100k\Omega$  if low quiescent power is a major factor and maximum bandwidth less important.

- (b) chosen to provide maximum gain-bandwidth product in Tr<sub>1</sub>.

- (c) reduced to about  $100\Omega$  if maximum output current is required.

$R_3$  may be reduced towards  $R_4/h_{FE}$  and  $R_2$  increased towards  $h_{FE}$ .  $R_1$ .

### Circuit modifications

- If the signal source can sink direct emitter current of  $Tr_1$ ,  $C_1$  and  $R_4$  may be omitted and the source connected directly to  $Tr_1$  emitter as shown left, the rest of the circuit remaining the same.

- Where d.c. isolation of the source and  $Tr_1$  emitter is required, an alternative input arrangement to the original circuit using a transformer may be adopted as shown centre, again the remaining circuitry being unchanged. This input transformer may be used to match the source to the input impedance of  $Tr_1$  if desired.

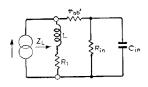

• If it is required to use a common-base stage that provides an output current which is as nearly identical to the input current as possible, a compound transistor may be used as shown right. The base current of  $\mathrm{Tr}_1$  is a very good measure of the extent by which its collector current falls short of its emitter current. By feeding back the base current of  $\mathrm{Tr}_1$  to the common-base transistor  $\mathrm{Tr}_3$  and adding its collector current to the input current, the output current more nearly approaches  $\mathrm{I_{in}}$ . This technique also raises the output impedance from  $\mathrm{Z_{out_1}}$  to approximately  $\mathrm{Z_{out_1}}.h_{\mathrm{fb_1}}/(1-h_{\mathrm{fb_3}})$  and reduces the distortion from  $\mathrm{D_1\%}$  to approximately  $\mathrm{D_1(1-h_{\mathrm{fb_3}})}$ % compared with  $\mathrm{Tr_1}$  alone.

#### Further reading

Miller, J. R., Solid-State Communications, McGraw-Hill 1966, chapter 15.

Boxall, F. S. Base current feedback and feedback compound transistor, *Semiconductor Products* vol. 1, no. 5, 1958, pp. 17-24.

#### Cross references

Series 12, cards 2, 5 & 9. Series 7, card 9.